Imager マニア

デジカメ / デジタルビデオカメラ / スマホ用の撮像素子(イメージセンサ/imager/CMOSセンサ)について、マニアな情報や私見を徒然なるままに述べるBlogです(^^;)

[PR]

×

[PR]上記の広告は3ヶ月以上新規記事投稿のないブログに表示されています。新しい記事を書く事で広告が消えます。

続・Sony 業界初、DRAMを積層した3層構造のCMOSイメージセンサー ~はたまたニコンの衝撃

”ニコン DLシリーズ発売中止”

いや、本当に驚きました。

発売延期が長引いてて、”随分苦戦してるんだな”とは思っていましたが、まさか発売中止になろうとは・・・

発売中止の判断理由の一つに”発売しても儲からない”みたいなのも入っていますが、

現状のコンパクトデジカメ市場で1インチ搭載機が無い状態で戦うというのもとても厳しいものに思え、”押すのも引くのも茨の道”な雰囲気を感じます。

なんとなく、株主へ向けての”改革断行してます!”みたいな経営陣のアピールの生贄の一つにされたのじゃないか?という気も、個人的に少ししなくもないですが・・・

更にニュースでは見ないのですが、

決算発表資料(p.14や16)を見ると、

”アクションカメラ「KeyMission」シリー ズ販売不振に伴い、想定販売台数 を⼤幅に引き下げ”

ですよね(^^;)

いや、本当に驚きました。

発売延期が長引いてて、”随分苦戦してるんだな”とは思っていましたが、まさか発売中止になろうとは・・・

発売中止の判断理由の一つに”発売しても儲からない”みたいなのも入っていますが、

現状のコンパクトデジカメ市場で1インチ搭載機が無い状態で戦うというのもとても厳しいものに思え、”押すのも引くのも茨の道”な雰囲気を感じます。

なんとなく、株主へ向けての”改革断行してます!”みたいな経営陣のアピールの生贄の一つにされたのじゃないか?という気も、個人的に少ししなくもないですが・・・

更にニュースでは見ないのですが、

決算発表資料(p.14や16)を見ると、

”アクションカメラ「KeyMission」シリー ズ販売不振に伴い、想定販売台数 を⼤幅に引き下げ”

ですよね(^^;)

PR

Sony 業界初、DRAMを積層した3層構造のCMOSイメージセンサー ~やはりスマホ向けでした

本日のblogタイトルは、あえてソニーの公式HP発表のままとさせて頂いています(^^;)

これ、今年は随分と各所で(ソニー以外の件も含めて)ISSCCの発表内容が取り上げられていますので、皆さん既にご存知かと思います。

(昨年まではここまで詳しく一般web媒体等でとりあげられたりしなかったと思うのですが、この違いは何なんでしょうか?世の中(技術業界?)でのイメージセンサの地位?が向上したという前向きな捉え方でOK?^^;)

ちなみにソニーもパナソニックも、ISSCC発表内容と同じと思われるものを、ISSCCでの発表”以降に”、自社HPで宣伝(?)し始めるのは、

ISSCCという学会(?)が特殊で、”まだ世の中に知られていない既知では無い内容しか投稿論文で受け付けず、また発表もさせない”というスタンスを取っているからだと思われます。

つまり、自社HPで先に発表予定のイメージセンサの凄さをアピールしちゃうと、その時点でISSCCでの発表権利を喪失してしまうため、早々に宣伝したいんだけどできなかったということかと。

ISSCCは、つまり他の学会で報告済みの発表案件を使いまわしで発表することを禁じているということも意味しており、だから?半導体学会の中でも最高のステータスを維持できているのかもしれませんね。

余談でした。

(↑上記厳密には事実では無いことを言っているかもしれませんが、細かいところはご容赦ください)

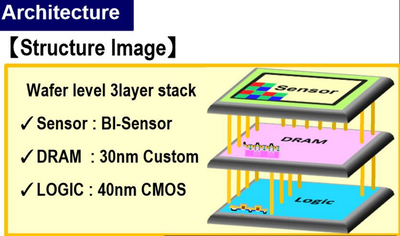

↑恐らくISSCCの発表で実際に使われたのではないかと思われるスライド

これ、今年は随分と各所で(ソニー以外の件も含めて)ISSCCの発表内容が取り上げられていますので、皆さん既にご存知かと思います。

(昨年まではここまで詳しく一般web媒体等でとりあげられたりしなかったと思うのですが、この違いは何なんでしょうか?世の中(技術業界?)でのイメージセンサの地位?が向上したという前向きな捉え方でOK?^^;)

ちなみにソニーもパナソニックも、ISSCC発表内容と同じと思われるものを、ISSCCでの発表”以降に”、自社HPで宣伝(?)し始めるのは、

ISSCCという学会(?)が特殊で、”まだ世の中に知られていない既知では無い内容しか投稿論文で受け付けず、また発表もさせない”というスタンスを取っているからだと思われます。

つまり、自社HPで先に発表予定のイメージセンサの凄さをアピールしちゃうと、その時点でISSCCでの発表権利を喪失してしまうため、早々に宣伝したいんだけどできなかったということかと。

ISSCCは、つまり他の学会で報告済みの発表案件を使いまわしで発表することを禁じているということも意味しており、だから?半導体学会の中でも最高のステータスを維持できているのかもしれませんね。

余談でした。

(↑上記厳密には事実では無いことを言っているかもしれませんが、細かいところはご容赦ください)

↑恐らくISSCCの発表で実際に使われたのではないかと思われるスライド

各社レンズ交換式デジカメ現役ラインナップ一覧と'16年発売機種リスト ~そしてISSCCでのソニー発表3層積層はホンモノの3層積層っぽい

今年二度目のblogエントリ時で既に2月(^^;)

本日からISSCC始まりますね。

本題とは離れますが、ISSCCに絡んで一つ。

以前、今回のISSCCでのソニー発表の”DRAM積層センサは、真の(?)3層積層センサなのか?”的なことを書きましたが、

どうやら真の3層積層センサの様ですね。

しばらく前のimage sensor worldさん経由の情報です↓

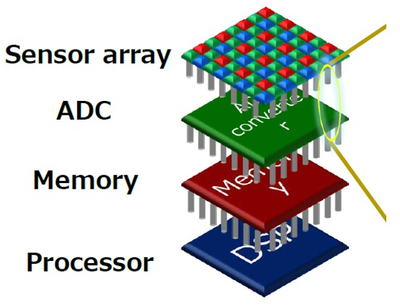

↑「これじゃ既に(?)4Layeredセンサじゃないか!」

という気がしますが、今回の発表ではDSPとメモリあたりが1レイヤーになっているのでしょうか?

個人的興味はこれが量産レベルなのか?というところですが、ソニーのことなので、”発表する時は量産可能”の法則(?)にこれも則っているのでしょうね。

本日からISSCC始まりますね。

本題とは離れますが、ISSCCに絡んで一つ。

以前、今回のISSCCでのソニー発表の”DRAM積層センサは、真の(?)3層積層センサなのか?”的なことを書きましたが、

どうやら真の3層積層センサの様ですね。

しばらく前のimage sensor worldさん経由の情報です↓

↑「これじゃ既に(?)4Layeredセンサじゃないか!」

という気がしますが、今回の発表ではDSPとメモリあたりが1レイヤーになっているのでしょうか?

個人的興味はこれが量産レベルなのか?というところですが、ソニーのことなので、”発表する時は量産可能”の法則(?)にこれも則っているのでしょうね。

'16年 コンパクト(≒レンズ固定式)デジタルカメラ各社発売機種数とラインナップ一覧

新年おめでとうございます。

遅いご挨拶となりましたが、本年も一応本blog続ける気はありますので(^^;)、何卒よろしくお願い致しますm(__)m

さて、世間ではCESやCP+に向けて、新機種の発表が始まっていますが、弊blogでは最新情報は追わず(?^^;)、例年恒例の昨年の振り返りシリーズです。

昨年までのエントリと合わせて見てみると、トレンドがわかっておもしろいかもしれませんのでどうぞ。

まずは、昨年の各社のコンパクトデジカメの売上台数の”計画”数ですが、決算資料などで公表しているのは以下三社の数字のみだと思います。

()内数字はいずれも対前年度増減率

Canon :400万台 (約40%減予測)

Nikon :335万台 (約46%減予測)

Olympus: 40万台 (約32%減予測)

Canonのみ'16年1月~12月。他2社は'16年4月~'17年3月の数字

上記以外の会社は、レンズ交換式との合算数値を公表している会社はありますが、コンパクトデジカメで独立した数字を出しているのは見つけられませんでした。

ちなみに、週明けの1/31にキヤノンは'16年決算発表がありますので、キヤノンに関してはあと数日で確定数が知れることになります。

参考までにCIPA統計ですが、こちらも恐らく2月に入れば'16年の数字が確定すると思われますが、微妙に間に合っておらず11月までの数字ですが、

各社合算の”出荷台数”ベースで、トータル:1118万3889台 @ワールドワイド

グラフを見ると、例年と異なった売上台数推移を見せていることがわかります。

(↑例年、コンパクトデジカメもレンズ交換式カメラも、10月に出荷台数ピークがくるのに、昨年は11月の方が増加している。12月はどうなったのか・・・?)

これは熊本の震災によるソニー撮像素子の出荷遅れもしくは数量減少と因果関係があるのでしょうか。

という訳で、どうやら昨年'16年の、レンズ固定式カメラの出荷台数は、なんとか1200万台前後の数字を確保していそうです。

'15年のレンズ固定式カメラの各社の総出荷台数が2234万1458台でしたから、

'16年は対'15年比で、大凡46%減 Σ(゜Д゜)!

という数字になりそうです。

恐らくこれは多くの会社で、予測値を更に下回る数字だと思いますf(^^;)

遅いご挨拶となりましたが、本年も一応本blog続ける気はありますので(^^;)、何卒よろしくお願い致しますm(__)m

さて、世間ではCESやCP+に向けて、新機種の発表が始まっていますが、弊blogでは最新情報は追わず(?^^;)、例年恒例の昨年の振り返りシリーズです。

昨年までのエントリと合わせて見てみると、トレンドがわかっておもしろいかもしれませんのでどうぞ。

まずは、昨年の各社のコンパクトデジカメの売上台数の”計画”数ですが、決算資料などで公表しているのは以下三社の数字のみだと思います。

()内数字はいずれも対前年度増減率

Canon :400万台 (約40%減予測)

Nikon :335万台 (約46%減予測)

Olympus: 40万台 (約32%減予測)

Canonのみ'16年1月~12月。他2社は'16年4月~'17年3月の数字

上記以外の会社は、レンズ交換式との合算数値を公表している会社はありますが、コンパクトデジカメで独立した数字を出しているのは見つけられませんでした。

ちなみに、週明けの1/31にキヤノンは'16年決算発表がありますので、キヤノンに関してはあと数日で確定数が知れることになります。

参考までにCIPA統計ですが、こちらも恐らく2月に入れば'16年の数字が確定すると思われますが、微妙に間に合っておらず11月までの数字ですが、

各社合算の”出荷台数”ベースで、トータル:1118万3889台 @ワールドワイド

グラフを見ると、例年と異なった売上台数推移を見せていることがわかります。

(↑例年、コンパクトデジカメもレンズ交換式カメラも、10月に出荷台数ピークがくるのに、昨年は11月の方が増加している。12月はどうなったのか・・・?)

これは熊本の震災によるソニー撮像素子の出荷遅れもしくは数量減少と因果関係があるのでしょうか。

という訳で、どうやら昨年'16年の、レンズ固定式カメラの出荷台数は、なんとか1200万台前後の数字を確保していそうです。

'15年のレンズ固定式カメラの各社の総出荷台数が2234万1458台でしたから、

'16年は対'15年比で、大凡46%減 Σ(゜Д゜)!

という数字になりそうです。

恐らくこれは多くの会社で、予測値を更に下回る数字だと思いますf(^^;)

'16年 民生ビデオカメラ各社発売機種数とラインナップ一覧

いつからクリスマスが何の変哲も無い日常になったのでしょう(^^;)

日常なのでblog更新です(笑)

クラブワールドカップで鹿島が思いもよらぬ(?)健闘を見せ、今年はさすがにもうカメラ等の発売も発表も無いでしょうから、年内イベントは(大晦日あたりの格闘技を除き)終わった感じでしょうか。

私的には仕事もそこまで忙しく無いため、なんとなく今年も終わりな気分になってきています。

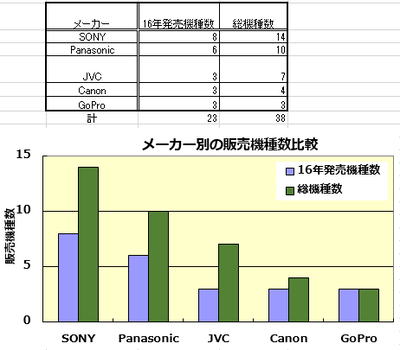

さて、ということで年末恒例企画?今年振り返りシリーズ第一弾、民生ビデオカメラ編。

昨年は、”つまらないのでもうやらない”と書いたのですが、なんだかんだで惰性で行ってしまいました(^^;)

本当は、360°カメラかアクションカム、または業務用カメラか監視カメラあたりをかわりにやってみたかったのですが、エネルギーが湧かずマンネリで自分でもつまらないのですが・・・

なので、例年ほどには詳細な撮像素子スペック等の分析(?)は行っていません。

各社の民生ビデオカメラのリスト化と所感のみです。

日常なのでblog更新です(笑)

クラブワールドカップで鹿島が思いもよらぬ(?)健闘を見せ、今年はさすがにもうカメラ等の発売も発表も無いでしょうから、年内イベントは(大晦日あたりの格闘技を除き)終わった感じでしょうか。

私的には仕事もそこまで忙しく無いため、なんとなく今年も終わりな気分になってきています。

さて、ということで年末恒例企画?今年振り返りシリーズ第一弾、民生ビデオカメラ編。

昨年は、”つまらないのでもうやらない”と書いたのですが、なんだかんだで惰性で行ってしまいました(^^;)

本当は、360°カメラかアクションカム、または業務用カメラか監視カメラあたりをかわりにやってみたかったのですが、エネルギーが湧かずマンネリで自分でもつまらないのですが・・・

なので、例年ほどには詳細な撮像素子スペック等の分析(?)は行っていません。

各社の民生ビデオカメラのリスト化と所感のみです。

↑ メーカー別の'16年 民生ビデオカメラの発売機種数

ブログ内検索

カウンター

最新コメント

[03/28 hoge]

[03/26 hi-low]

[03/22 山川]

[03/18 hoge]

[03/08 hi-low]

[03/04 hoge]

[02/26 山川]

[02/26 山川]

[02/19 hoge]

[02/18 山川]

[02/05 hoge]

[02/05 hi-low]

[01/29 通りすがりです]

[01/28 FT]

[01/23 hi-low]

カテゴリー

カレンダー

最新記事

(04/22)

(04/01)

(03/25)

(03/17)

(03/11)

最古記事

プロフィール

HN:

imagerマニア

性別:

非公開