Imager マニア

デジカメ / デジタルビデオカメラ / スマホ用の撮像素子(イメージセンサ/imager/CMOSセンサ)について、マニアな情報や私見を徒然なるままに述べるBlogです(^^;)

[PR]

×

[PR]上記の広告は3ヶ月以上新規記事投稿のないブログに表示されています。新しい記事を書く事で広告が消えます。

ソニー 8Mpix / 480fps Gain-Adaptive列AD? 2-on1 stacked device structure? ~VLSIシンポジウムプログラムより 今月のNABでソニーより4K480pの業務用カムコーダー発表?

今週書きたいのはタイトルの件なのですが、その前に(^^;)

先週のGalaxyS7に続いて、チップワークスでiPhoneSEの簡単な分解レポートが出されています。

それによると、

◆メインカメラ(≒リアカメラ)搭載撮像素子はソニー製で、iPhone6sと同じもの

◆サブカメラ(≒フロントカメラ=FaceTimeカメラ)搭載撮像素子はOmniVision製裏面照射型で

・型番 :OV2E0BNN

・画素数 :1.2M

・画素ピッチ :1.75um□

・チップサイズ:4.3 mm x 4.1 mm ≒ 17.6 mm2

参考:カメラモジュールサイズ:6.0 mm x 5.5 mm x 3.8 mm 厚

となっていたようです。

これを見ると、iPhoneSEのカメラ(撮像素子)に関してのトピックは、

”iPhone5s以来、オムにビジョンがソニーからFaceTimeカメラ搭載撮像素子の座は取り戻した”

ということでしょうか。

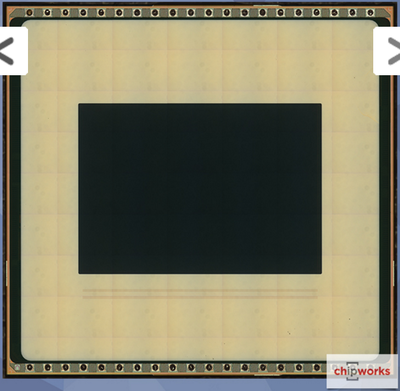

↑ OmniVision製 1.2Mpix裏面照射型センサ 上面顕微鏡写真 チップワークスblogより

先週のGalaxyS7に続いて、チップワークスでiPhoneSEの簡単な分解レポートが出されています。

それによると、

◆メインカメラ(≒リアカメラ)搭載撮像素子はソニー製で、iPhone6sと同じもの

◆サブカメラ(≒フロントカメラ=FaceTimeカメラ)搭載撮像素子はOmniVision製裏面照射型で

・型番 :OV2E0BNN

・画素数 :1.2M

・画素ピッチ :1.75um□

・チップサイズ:4.3 mm x 4.1 mm ≒ 17.6 mm2

参考:カメラモジュールサイズ:6.0 mm x 5.5 mm x 3.8 mm 厚

となっていたようです。

これを見ると、iPhoneSEのカメラ(撮像素子)に関してのトピックは、

”iPhone5s以来、オムにビジョンがソニーからFaceTimeカメラ搭載撮像素子の座は取り戻した”

ということでしょうか。

↑ OmniVision製 1.2Mpix裏面照射型センサ 上面顕微鏡写真 チップワークスblogより

また、全くの憶測で書いてしまいますが、

今回フロントカメラ搭載撮像素子だけ再びオムニビジョン製に戻った件、

”SE”はアップルにとっては”チープにしたくは無いけどコストダウンはしたい”という機種だったんじゃないかと思うのですが、

単純にコストダウン、すなわち恐らく今でも”ソニー製の素子よりもOmni製の素子の方がお安く手に入るから”

という理由だったんじゃないかと勝手に予想します(明らかにチップサイズが小さくなっているからというのもありますが・・・)。

リアカメラは性能ケチれないけど、FaceTimeカメラならスペックケチっても気にする人少ないかな・・・という(^^;)

あとはメインカメラの方は変わりませんが、iPhone6s解析時よりも、チップワークスさんが解像度の良い写真を載せてくれているというのもわずかなトピックと言えばトピックです(^^;)

さて、本題に移りたいと思います。

毎年6月に開催されるVLSIシンポジウム。

開催場所はハワイと京都の持ち回りなのですが、今年はハワイの番。

昨年はイメージセンサとしては、オリンパスが”16Mpixの積層グローバルシャッタセンサ”を発表した、半導体の国際学会(?)となります

そのプログラムが、先月末に発表されました。

”Technology”と”Circuits”の2種類に大別されるのですが、

”テクノロジー”の方は、今年は”プロセス技術を10nm以下に微細化するための革新技術”に関する発表が多数される様です。

”More Moore” どこまでいけるのでしょうか?

で、今回の弊blogエントリで注目なのが、”Curcuits”の方の95番

悔しいかな(?)2週続けてになってしまうのですが、やはりソニーさんの件です(^^;)

昨年一年間は、主要な国際学会で発表することなく沈黙を守っていた(?)ソニーですが、

今回遂に満を持して(?)以下タイトルで発表があるようです。

「An 8.3M‐pixel 480fps Global‐Shutter CMOS Image Sensor with Gain‐Adaptive Column ADCs and 2‐on‐1 Stacked Device Structure」

タイトルだけで気になる点が複数あるのですが、

先に結論を記載すると、個人的にはかなりな確率で、

このNABで新しく発表されるカメラ搭載の撮像素子が、6月にVLSIシンポジウムで発表予定の上記ソニーの素子なのではと思っています。

まず、ソニーは過去にもISSCCにおいて発表したセンサを業務用カメラに恐らくそのまますぐに搭載した事例というのがあります

ISSCC2011 → CineAltaF65

ISSCC2012 → CineAltaF55

なので、今回発表センサも何かのカメラに搭載される可能性が高いのではないかな?と。

そして、別のインタビューで、ソニーの方が「NABで8倍速スローが可能な超ハイスピードな新しい4Kカメラを発表する」と明言されています。

NABとは今月半ばからアメリカ ラスベガスで開催される世界一の(?)放送機器展の様なものなのですが、

インタビューの原文では以下の様な表現になっています。

「At the show, Sony will also debut their newest Ultra HFR camera, building on the success of the HDC-4300 and other popular studio camera systems. This new camera will offer up to 8x high frame rate in 4K」

発表タイトルの方の”8.3M-Pixel”ですが、これは

3840×2160=8294400 ≒ 8.3M

なので、ほぼ間違い無く4Kセンサだと思われます。

この画素数のセンサを何かの製品に搭載するとすると、一眼レフやミラーレス、コンパクトデジカメ向けにはさすがにきょうび画素数が不足していて厳しいので、まず動画専用カメラに搭載されるものと推定できます。

また”480fps”の方ですが、この発表タイトルからは、明らかに8.3M画素時に480fpsを出すという風に読めます。

(もしこれで、”480fps時はFHDまでしか読めません”ではタイトルに偽りありの非難が出ると思いますので^^;)

つまり4K/480fpsな訳ですが、この信号読み出しrateは、上記ミラーレスなどもそうですが、民生向けのカムコーダーでは、(4K/60pに四苦八苦している現状では)

バッテリ / 発熱 / 信号処理速度 / メディアの書き込み速度 / 価格

いずれもまだ対応不能でまともな大きさの製品になる気がしません(^^;)

それに、まだ民生用ではさすがに4K480fpsの需要がありません(^^;)

ですので、何かのカメラにこの発表センサが搭載されるなら、この時点でほぼ業務用の動画カメラであろうと思います。

他方、上記ソニーの方のインタビュー発言ですが、

”ウルトラハイフレームレートな≒8倍スロー可能な”新しいカメラの方は、

NABで発表する時点でほぼ動画カメラであることが確定です。

更に、”8倍スロー”のベースとなっているフレームレートがいくつかで、このカメラの4K時の最大フレームレートがわかるのですが、可能性は以下3通り

1) 24fps × 8 = 192fps

2) 30fps × 8 = 240fps

3) 60fps × 8 = 480fps

で、ソニーの方のインタビューの回答は「HDC-4300や他のスタジオカメラの成功を受けて」カメラを発表するとのことなので、スタジオカメラ(≒放送)基準で考えている可能性が大なのかなと思うのと、ウルトラまでつけちゃう(^^;)ほどのスピードという二つの観点から、

3)の60pベースの8倍スローの可能性が高いのではないかと。

上記推測が正しいとすると、NABで発表されるカメラは、”4K/480fps可能な業務用動画カメラ”となり、今回のVLSIシンポジウムでソニーが発表するセンサの仕様と一致します。

上記までが、VLSIシンポジウムでソニーが発表するセンサが、NABでソニーが発表する新しいカメラ搭載撮像素子ではないかと私が思う理由です。

ここからはNABで発表されるカメラのことは置いておいて、VLSIシンポジウムで発表されるソニーのセンサのことですが、

8.3M と 480fps 以外に発表タイトルに残っている要素として、以下があります。

①グローバルシャッター

②Gain‐Adaptive Column ADCs (ゲイン適応列ADC?)

③ 2‐on‐1 Stacked Device Structure (1チップ上に二つの素子が載った積層センサ?)

まあ①はこの際置いておきます(^^;)

一般的にはまだそこそこのトピックですが、もうソニーCineAltaF55では既にグローバルシャッタセンサが採用された実績がありますし、

シネマ及び放送用業務カメラとしては、ブラックマジックデザインが結構な機種数のカメラをグローバルシャッタで製品化している実績が既にあります。

(↑しかしつい最近の機種で、URSA mini 4.6Kとマイクロシネマカメラでは、自慢の?グローバルシャッタ動作モードは不具合があるため、仕様から消すという発表を行っていましたが^^;)

問題は(≒私が今興味あるのは)②と③で、

まずは②は文言からはパッと何が言いたいのかイメージがわかりません(^^;)。

()内に書いた様に、直訳すれば”ゲイン適応列ADC”ということになるのでは?と思うのですが、”ゲイン適応列ADCって何?”という感じです(^^;)

ひとまず”ゲイン適応 ソニー”とか”Gain‐Adaptive Column ADC Sony”とかでググッてみて出てくるのがコレです。

が、これ、2003年(≒13年前)のISSCC発表の技術で、

また”Pixel-Gain-Adaptive Column Amplifier(アンプ)”技術であり、ADC技術では無い様なので、

ちょっと今回ソニーがVLSIシンポジウムで発表する内容とは違うと思います。

という訳で、残念ながらこれはちょっとヒントがなくてわからないので仕方なく置いておくとして(^^;)、

するとタイトルの中で個人的に最も興味深い点が残り、それが③です。

③ 2‐on‐1 Stacked Device Structure

私、英語不得意ですが・・・↑これ、タイトルつけ間違いとかじゃなければ、どう見ても一つのでかいチップの上に、それよりかは小さいサイズのチップが”2つ”載ってますよね?f(^^;)

もう軽くパニックなんですが(^^;)、自分が疑問に思うことを冷静に整理すると・・・

ⅰ)そういう構造にする必要性は?

ⅱ)どういうくっつけ方してるの?

の二つの観点に集約される気がします。

前者のⅰ)の方で思いつくのは、

ⅰ)-1:RX100M4とRX10M2の1インチ裏面照射型積層センサのパッケージ裏面についていたDRAMを、3チップ目として積層した

もしくは、

ⅰ)-2:シネマ用でsuper35mmフォーマットセンサである(と仮定)。故にまだ今までのソニーのExmorRSの積層センサはサイズ的に難しかった(←動画の10:00~11:00) ⇒ しかし速度等の観点から?積層にする必要があったので、別の方法での積層化への道を探った結果

ⅱ)の方ではっきりしているのは、仮に想像通り、1チップの上に小さ目の2チップが載っている構造の場合、製造時のwafer to wafer のボンディング(←お互いウェハの状態のまま貼り合わせること)は不可能だと思われます。

最悪はそれぞれがチップの状態にダイシング(←切り分けられた)後に、3チップを何らかの方法で積層するか、

良くて、母体の1チップ側はウェハ状態で、残り上に載せる(?)2チップは、チップ状態にダイシング後に何らかの方法で積層されるか。

いずれにしても、今までの積層方法よりもコストが掛かることは間違い無いと思われます。

この構造であることも、今回発表されるセンサが(数を作らなければならない)ひとまず民生用カメラ向けでは無いだろうという予測の一つの理由です。

で、くっつけ方そのものは、先週エントリしたソニーIMX260で採用されていたCu-Cuの直接ボンディング、

あれはまだ今回のこの様な構造のセンサへの適用は無理なのではと思います。

それどころか、恐らく従来の積層センサで採用されていたTSVによる積層もまだ難しいのでは?・・・という気がします。

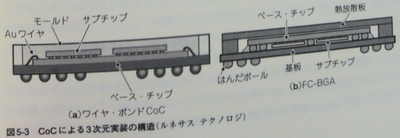

ではどんな構造してると思ってるんだ?と言いますと、手元のこの教科書に載っていた図ですが、

例えばこんなの↓とか

↑右のも左のも、上下が逆になったりしてはいますが、基本母体のチップにサブチップ2チップがマイクロ(微小)バンプと呼ばれる、いやゆる半田の様なもので接続しているパターン

それとも、もはや変則の2チップ載せの積層チップも、従来通りTSV積層が既にソニーの手に掛かれば出来てしまっているものなのか・・・

全くまとまり無く、何が言いたかったのか理解して頂けない終わり方だなと思いますが、

とにかくまずはVLSIシンポジウムで発表されるソニーの新センサには個人的には注目ですというお話です(^^;)

もちろん他にも東北大等も発表することになっているようで、そちらもタイトルからすると今度は画素AD搭載センサな様子なので要注目なのですが、ひとまず今回はソニーの方がやはり製品化も極めて近そうな匂いを感じましたので取り上げてみました。

追加で何か気づいたことがあれば書き足すようにします。

今回フロントカメラ搭載撮像素子だけ再びオムニビジョン製に戻った件、

”SE”はアップルにとっては”チープにしたくは無いけどコストダウンはしたい”という機種だったんじゃないかと思うのですが、

単純にコストダウン、すなわち恐らく今でも”ソニー製の素子よりもOmni製の素子の方がお安く手に入るから”

という理由だったんじゃないかと勝手に予想します(明らかにチップサイズが小さくなっているからというのもありますが・・・)。

リアカメラは性能ケチれないけど、FaceTimeカメラならスペックケチっても気にする人少ないかな・・・という(^^;)

あとはメインカメラの方は変わりませんが、iPhone6s解析時よりも、チップワークスさんが解像度の良い写真を載せてくれているというのもわずかなトピックと言えばトピックです(^^;)

さて、本題に移りたいと思います。

毎年6月に開催されるVLSIシンポジウム。

開催場所はハワイと京都の持ち回りなのですが、今年はハワイの番。

昨年はイメージセンサとしては、オリンパスが”16Mpixの積層グローバルシャッタセンサ”を発表した、半導体の国際学会(?)となります

そのプログラムが、先月末に発表されました。

”Technology”と”Circuits”の2種類に大別されるのですが、

”テクノロジー”の方は、今年は”プロセス技術を10nm以下に微細化するための革新技術”に関する発表が多数される様です。

”More Moore” どこまでいけるのでしょうか?

で、今回の弊blogエントリで注目なのが、”Curcuits”の方の95番

悔しいかな(?)2週続けてになってしまうのですが、やはりソニーさんの件です(^^;)

昨年一年間は、主要な国際学会で発表することなく沈黙を守っていた(?)ソニーですが、

今回遂に満を持して(?)以下タイトルで発表があるようです。

「An 8.3M‐pixel 480fps Global‐Shutter CMOS Image Sensor with Gain‐Adaptive Column ADCs and 2‐on‐1 Stacked Device Structure」

タイトルだけで気になる点が複数あるのですが、

先に結論を記載すると、個人的にはかなりな確率で、

このNABで新しく発表されるカメラ搭載の撮像素子が、6月にVLSIシンポジウムで発表予定の上記ソニーの素子なのではと思っています。

まず、ソニーは過去にもISSCCにおいて発表したセンサを業務用カメラに恐らくそのまますぐに搭載した事例というのがあります

ISSCC2011 → CineAltaF65

ISSCC2012 → CineAltaF55

なので、今回発表センサも何かのカメラに搭載される可能性が高いのではないかな?と。

そして、別のインタビューで、ソニーの方が「NABで8倍速スローが可能な超ハイスピードな新しい4Kカメラを発表する」と明言されています。

NABとは今月半ばからアメリカ ラスベガスで開催される世界一の(?)放送機器展の様なものなのですが、

インタビューの原文では以下の様な表現になっています。

「At the show, Sony will also debut their newest Ultra HFR camera, building on the success of the HDC-4300 and other popular studio camera systems. This new camera will offer up to 8x high frame rate in 4K」

発表タイトルの方の”8.3M-Pixel”ですが、これは

3840×2160=8294400 ≒ 8.3M

なので、ほぼ間違い無く4Kセンサだと思われます。

この画素数のセンサを何かの製品に搭載するとすると、一眼レフやミラーレス、コンパクトデジカメ向けにはさすがにきょうび画素数が不足していて厳しいので、まず動画専用カメラに搭載されるものと推定できます。

また”480fps”の方ですが、この発表タイトルからは、明らかに8.3M画素時に480fpsを出すという風に読めます。

(もしこれで、”480fps時はFHDまでしか読めません”ではタイトルに偽りありの非難が出ると思いますので^^;)

つまり4K/480fpsな訳ですが、この信号読み出しrateは、上記ミラーレスなどもそうですが、民生向けのカムコーダーでは、(4K/60pに四苦八苦している現状では)

バッテリ / 発熱 / 信号処理速度 / メディアの書き込み速度 / 価格

いずれもまだ対応不能でまともな大きさの製品になる気がしません(^^;)

それに、まだ民生用ではさすがに4K480fpsの需要がありません(^^;)

ですので、何かのカメラにこの発表センサが搭載されるなら、この時点でほぼ業務用の動画カメラであろうと思います。

他方、上記ソニーの方のインタビュー発言ですが、

”ウルトラハイフレームレートな≒8倍スロー可能な”新しいカメラの方は、

NABで発表する時点でほぼ動画カメラであることが確定です。

更に、”8倍スロー”のベースとなっているフレームレートがいくつかで、このカメラの4K時の最大フレームレートがわかるのですが、可能性は以下3通り

1) 24fps × 8 = 192fps

2) 30fps × 8 = 240fps

3) 60fps × 8 = 480fps

で、ソニーの方のインタビューの回答は「HDC-4300や他のスタジオカメラの成功を受けて」カメラを発表するとのことなので、スタジオカメラ(≒放送)基準で考えている可能性が大なのかなと思うのと、ウルトラまでつけちゃう(^^;)ほどのスピードという二つの観点から、

3)の60pベースの8倍スローの可能性が高いのではないかと。

上記推測が正しいとすると、NABで発表されるカメラは、”4K/480fps可能な業務用動画カメラ”となり、今回のVLSIシンポジウムでソニーが発表するセンサの仕様と一致します。

上記までが、VLSIシンポジウムでソニーが発表するセンサが、NABでソニーが発表する新しいカメラ搭載撮像素子ではないかと私が思う理由です。

ここからはNABで発表されるカメラのことは置いておいて、VLSIシンポジウムで発表されるソニーのセンサのことですが、

8.3M と 480fps 以外に発表タイトルに残っている要素として、以下があります。

①グローバルシャッター

②Gain‐Adaptive Column ADCs (ゲイン適応列ADC?)

③ 2‐on‐1 Stacked Device Structure (1チップ上に二つの素子が載った積層センサ?)

まあ①はこの際置いておきます(^^;)

一般的にはまだそこそこのトピックですが、もうソニーCineAltaF55では既にグローバルシャッタセンサが採用された実績がありますし、

シネマ及び放送用業務カメラとしては、ブラックマジックデザインが結構な機種数のカメラをグローバルシャッタで製品化している実績が既にあります。

(↑しかしつい最近の機種で、URSA mini 4.6Kとマイクロシネマカメラでは、自慢の?グローバルシャッタ動作モードは不具合があるため、仕様から消すという発表を行っていましたが^^;)

問題は(≒私が今興味あるのは)②と③で、

まずは②は文言からはパッと何が言いたいのかイメージがわかりません(^^;)。

()内に書いた様に、直訳すれば”ゲイン適応列ADC”ということになるのでは?と思うのですが、”ゲイン適応列ADCって何?”という感じです(^^;)

ひとまず”ゲイン適応 ソニー”とか”Gain‐Adaptive Column ADC Sony”とかでググッてみて出てくるのがコレです。

が、これ、2003年(≒13年前)のISSCC発表の技術で、

また”Pixel-Gain-Adaptive Column Amplifier(アンプ)”技術であり、ADC技術では無い様なので、

ちょっと今回ソニーがVLSIシンポジウムで発表する内容とは違うと思います。

という訳で、残念ながらこれはちょっとヒントがなくてわからないので仕方なく置いておくとして(^^;)、

するとタイトルの中で個人的に最も興味深い点が残り、それが③です。

③ 2‐on‐1 Stacked Device Structure

私、英語不得意ですが・・・↑これ、タイトルつけ間違いとかじゃなければ、どう見ても一つのでかいチップの上に、それよりかは小さいサイズのチップが”2つ”載ってますよね?f(^^;)

もう軽くパニックなんですが(^^;)、自分が疑問に思うことを冷静に整理すると・・・

ⅰ)そういう構造にする必要性は?

ⅱ)どういうくっつけ方してるの?

の二つの観点に集約される気がします。

前者のⅰ)の方で思いつくのは、

ⅰ)-1:RX100M4とRX10M2の1インチ裏面照射型積層センサのパッケージ裏面についていたDRAMを、3チップ目として積層した

もしくは、

ⅰ)-2:シネマ用でsuper35mmフォーマットセンサである(と仮定)。故にまだ今までのソニーのExmorRSの積層センサはサイズ的に難しかった(←動画の10:00~11:00) ⇒ しかし速度等の観点から?積層にする必要があったので、別の方法での積層化への道を探った結果

ⅱ)の方ではっきりしているのは、仮に想像通り、1チップの上に小さ目の2チップが載っている構造の場合、製造時のwafer to wafer のボンディング(←お互いウェハの状態のまま貼り合わせること)は不可能だと思われます。

最悪はそれぞれがチップの状態にダイシング(←切り分けられた)後に、3チップを何らかの方法で積層するか、

良くて、母体の1チップ側はウェハ状態で、残り上に載せる(?)2チップは、チップ状態にダイシング後に何らかの方法で積層されるか。

いずれにしても、今までの積層方法よりもコストが掛かることは間違い無いと思われます。

この構造であることも、今回発表されるセンサが(数を作らなければならない)ひとまず民生用カメラ向けでは無いだろうという予測の一つの理由です。

で、くっつけ方そのものは、先週エントリしたソニーIMX260で採用されていたCu-Cuの直接ボンディング、

あれはまだ今回のこの様な構造のセンサへの適用は無理なのではと思います。

それどころか、恐らく従来の積層センサで採用されていたTSVによる積層もまだ難しいのでは?・・・という気がします。

ではどんな構造してると思ってるんだ?と言いますと、手元のこの教科書に載っていた図ですが、

例えばこんなの↓とか

↑右のも左のも、上下が逆になったりしてはいますが、基本母体のチップにサブチップ2チップがマイクロ(微小)バンプと呼ばれる、いやゆる半田の様なもので接続しているパターン

それとも、もはや変則の2チップ載せの積層チップも、従来通りTSV積層が既にソニーの手に掛かれば出来てしまっているものなのか・・・

全くまとまり無く、何が言いたかったのか理解して頂けない終わり方だなと思いますが、

とにかくまずはVLSIシンポジウムで発表されるソニーの新センサには個人的には注目ですというお話です(^^;)

もちろん他にも東北大等も発表することになっているようで、そちらもタイトルからすると今度は画素AD搭載センサな様子なので要注目なのですが、ひとまず今回はソニーの方がやはり製品化も極めて近そうな匂いを感じましたので取り上げてみました。

追加で何か気づいたことがあれば書き足すようにします。

PR

コメント

ブログ内検索

カウンター

最新コメント

[03/28 hoge]

[03/26 hi-low]

[03/22 山川]

[03/18 hoge]

[03/08 hi-low]

[03/04 hoge]

[02/26 山川]

[02/26 山川]

[02/19 hoge]

[02/18 山川]

[02/05 hoge]

[02/05 hi-low]

[01/29 通りすがりです]

[01/28 FT]

[01/23 hi-low]

カテゴリー

カレンダー

最新記事

(04/22)

(04/01)

(03/25)

(03/17)

(03/11)

最古記事

プロフィール

HN:

imagerマニア

性別:

非公開