Imager マニア

デジカメ / デジタルビデオカメラ / スマホ用の撮像素子(イメージセンサ/imager/CMOSセンサ)について、マニアな情報や私見を徒然なるままに述べるBlogです(^^;)

[PR]

×

[PR]上記の広告は3ヶ月以上新規記事投稿のないブログに表示されています。新しい記事を書く事で広告が消えます。

キヤノン 外販用グローバルシャッタCMOSイメージセンサ(と思われる) ~ISSCC2017より

また一週blog更新が空いてしまいました(^^;)

今年も早いもので、もう卒業・入学式シーズン。日本ではカメラが最も売れる時(?)でしょうか?

という訳でも無いでしょうが、ワールドワイドでは今年の1月は近年稀に見る絶好調なカメラの販売状況(正確には出荷状況ですが)の様子です。

レンズ交換式カメラに至っては、前年同月比プラスに加えて、2年前の'15年1月をも上回った様です。

コンパクトデジカメの減少幅も約7%と、こちらも各社年間通した想定減少幅と比べれば、恐らく小さな値で収まっていそう。

恐らくデジカメ分野は、民生用途のイメージセンサ市場としては、スマホ、タブレット&pcに次ぐ3番目に大きな市場だと思いますので(←違いますかね?)結構なことだと思います(^^)

今回は、まず2回前の弊blogのソニーの3層積層型イメージセンサに関する記載の訂正から(^^;)

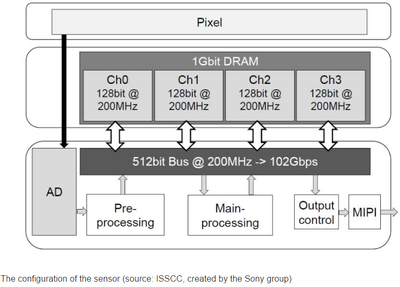

↑日経のサイトから。図の下の記載から、大元の出典はソニーの今年のISSCCの恐らくプレゼン資料から

3層積層センサのデータフロー図

既にコメント欄で情報及びご指摘頂いていますが、私は2回前のエントリで、

「DRAMへのアクセスはセンサ基板とロジック基板双方から行っているのだからDRAMを真ん中の層へ配置するのは何が疑問なんだろう?」

という様なニュアンスのコメントを書きました。

しかし、上図を見ると、(というか、上図を見ずとも過去のソニーの積層センサの多くは、)列ADC回路をbottomのロジック基板に配置してあるため、

データフローとしては、イメージセンサからのアナログ信号をロジック基板にまず通してしまうので、

その後、センサ基板(フォトダイオード配置基板)からDRAMに何かアクセスする必要性が発生しません。

故に、私の上記記載は、DRAM基板が真ん中に配置される理由には全くなり得ないことがわかります。

であるならば、後は私が思いつくDRAMが真ん中に配置される必然性と言えば、

今年も早いもので、もう卒業・入学式シーズン。日本ではカメラが最も売れる時(?)でしょうか?

という訳でも無いでしょうが、ワールドワイドでは今年の1月は近年稀に見る絶好調なカメラの販売状況(正確には出荷状況ですが)の様子です。

レンズ交換式カメラに至っては、前年同月比プラスに加えて、2年前の'15年1月をも上回った様です。

コンパクトデジカメの減少幅も約7%と、こちらも各社年間通した想定減少幅と比べれば、恐らく小さな値で収まっていそう。

恐らくデジカメ分野は、民生用途のイメージセンサ市場としては、スマホ、タブレット&pcに次ぐ3番目に大きな市場だと思いますので(←違いますかね?)結構なことだと思います(^^)

今回は、まず2回前の弊blogのソニーの3層積層型イメージセンサに関する記載の訂正から(^^;)

↑日経のサイトから。図の下の記載から、大元の出典はソニーの今年のISSCCの恐らくプレゼン資料から

3層積層センサのデータフロー図

既にコメント欄で情報及びご指摘頂いていますが、私は2回前のエントリで、

「DRAMへのアクセスはセンサ基板とロジック基板双方から行っているのだからDRAMを真ん中の層へ配置するのは何が疑問なんだろう?」

という様なニュアンスのコメントを書きました。

しかし、上図を見ると、(というか、上図を見ずとも過去のソニーの積層センサの多くは、)列ADC回路をbottomのロジック基板に配置してあるため、

データフローとしては、イメージセンサからのアナログ信号をロジック基板にまず通してしまうので、

その後、センサ基板(フォトダイオード配置基板)からDRAMに何かアクセスする必要性が発生しません。

故に、私の上記記載は、DRAM基板が真ん中に配置される理由には全くなり得ないことがわかります。

であるならば、後は私が思いつくDRAMが真ん中に配置される必然性と言えば、

”信号データの最終出力回路(上図でいうと、Output controlとMIPI)をロジック基板に配置しているため、ロジック基板は一番上(top)か一番下(bottom)に積層したい”

(↑middle層に配置してしまうと、ロジックチップだけチップサイズを大きくするとかいう相当イレギュラーなことを行わない限り、最終的に信号データを取り出す出力パッドを配置出来ず、信号を取り出せなくなってしまう)

⇒”他方、センサ基板は受光部なので、一番上(top)に配置するしか無い”

⇒すると、後は消去法で、ロジック基板がbottomで、DRAM基板がmiddleになる

・・・という感じでしょうか?

”最終出力回路をDRAM基板に作りこめないのか?”

”最終出力回路を作りこむ場所は、DRAM基板では無くロジック基板の方が適切なのか?”

と言ったことは私はわかりません。

ただ何となくですが、DRAM自体はソニーは自分で手がけていないことから、

DRAM基板については、なるべくシンプルに本来のDRAMとしての機能に特化したチップにしたかったのかな?とかは思います。

さて、今回は、今年のISSCC2017でキヤノン発表のグローバルシャッタセンサでわかっている情報を載せてみたいと思います。

ちなみにキヤノンでグローバルシャッタセンサと言えば・・・

何故か発売延期になっていた、CINEMA EOS C700 GSモデル

及び

少し前に始めたイメージセンサの外販事業対象の3製品の内の一つ

というところが思い浮かびます。

今回のISSCC発表の方は、(後のスペック表に出てきますが、)3.4um□画素ピッチ&約5Mpix画素数センサということで、

どうやら上記後者の方のイメージセンサに関しての様子です。

↑資料のソースその1は、相変わらずImageSensorsWorldさんより

これも恐らく実際のキヤノンのプレゼン資料なのでしょうね。

”Motivation”

”開発の動機”というところでしょうか。

資料内容からすると、

”ローリングシャッターセンサは、ローリングシャッタ歪やフラッシュバンド現象が発生するので、グローバルシャッタセンサが求められている”

”画素アーキテクチャとして、赤字の素子を、従来のローリングシャッタセンサに対して画素部に追加した”

”従来のローリングシャッタセンサは、ローリングシャッタ歪に制約(ネガ)があった。

従来のグローバルシャッタセンサは、飽和、ノイズ、感度に制約(ネガ)があった

我々の開発のゴールは、それらを克服した高性能なグローバルシャッタセンサ画素を得ること”

追加素子の赤字略称はそれぞれ・・・

MEM:メモリ

OFD:オーバーフロードレイン (フォトダイオードから溢れ出した余剰電荷を捨てる排出口)

OG:オーバーフローゲート?

GS:グローバルシャッタ・・・の略でしょうか。

画素アーキテクチャ(私の表現で言うと、画素の等価回路図)は、

ソニーのグローバルシャッタセンサのタイプ(と私が予想しているもの)に近いですね、各トランジスタスイッチの名称は、それぞれの会社によって呼び方が異なる様ですが。

他には、グローバルシャッタが得意な(?)CMOSISセンサなどがありますが、CMOSISのものとは明らかに等価回路図レベルで異なるものになっています。

↑出典は同様 内容ぎっしりですね。クリックして拡大しないと見えません(^^;)

”Architecture”

直訳すると”構造”という感じでしょうか。

一番上が”Multiple-Accumulation Shutter Technique”なので、

個人的に最大の謎だった”複数蓄積シャッター技術”なるものの説明箇所。

左が従来センサ、右がキヤノンの技術・・・なのですが、如何せんImageSensorsWorldさんのoriginalを拡大してみても、若干解像度悪く・・・

とにかく読み出し速度が2倍になっていて、従来1回蓄積なところを2回蓄積している・・・というのは文字から読み取れるのですが、図が何を言いたいのかは・・・(^^;)

一番の関心事である複数回蓄積のメリットや狙いは理解出来ず(--;)

上資料左側中段”BlockDiagram”から読み取れることは、

・2画素でFD(フローティングディフュージョン:拡散容量)や画素内アンプを共有している

・出力IFは、Sub-LVDS 12bit7(←に見える)Laneが上下に一つずつ

同様に左下”Wide Aperture Light Guide”(広開口光導波路)では、

どうやら、感度アップ(維持)とPLS(寄生感度:まだ読み出し前の、前フレームの信号電荷を保存している画素内メモリ部に、遮光性能の不足等の理由による迷光のために、ノイズとして見えてしまう感度成分。低い値の方が良い性能)性能アップのために、

Light Guideと呼ぶ光導波路構造を採用した と。

お陰で特に入射角度のついた光線に対する感度downを避けることが可能になっている・・・という図に見えます。

光導波路構造については、後日part2エントリ予定の日経の別記事の図の方がわかりやすそうです。

で、上プレゼン資料の右側なのですが・・・

これもちょっと解説無しは厳しい(--;)

SS-ADCはSingle Slope ADCで、AD変換方式のことを言っており、Dual Gain Column Ampは、2つのゲインを持つ列アンプ。

で、等価回路図も列アンプの後にSS-ADCが接続されているものになっている様で、

また波形図には明らかにSS-ADCのランプ波形(三角形のもの)が記載されており、他方赤い線と青い線の列アンプの出力信号と思われるものが見えます。

が、特に赤い線の方が不自然にぐにゃっと途中で曲がる線になっており、

この2本の線がDual-Gainを意味していそうではありますが、果たしてその意味するところは・・・

結果として、文字を読むと、

この方式によって、

・ハイフレームレート (≒高速信号読み出し)

・低消費電力

の両立が図られている・・・ということの様です。

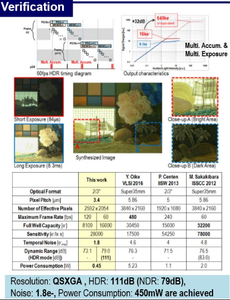

↑ImageSensorsWorldさん最後の資料

”Verification”

直訳すると”検証”

まあ、実験結果、実測確認といったところでしょうか。

右上の図からすると、

single蓄積時に8100e-(Electron:電子)の飽和電子数であるものが、

・Multi蓄積時(実際には2回蓄積の様子ですが、)に倍の16200e-の飽和電子数

になり、更には、

・長露光(8.3mSec)と短露光(84uSec)の合成によるHDR処理後には、64万e-飽和電子数相当

の画像になり、

HDR処理により+32dBのダイナミックレンジの拡大が図られましたよ

ということの様です。

その下の画像は、元資料の解像度が無いことに加え、そもそもoriginal画像を見なければwebで圧縮されたようなものを見ても正しい評価は出来ませんので、基本スルーというか本当に参考までという感じですが、

”明るいところ/暗いところ、きっちり飛ばずに/潰れずに表現できてるでしょ”

というアピールです。

しかしそれはキヤノンもわかってのことか、ISSCC当日は、来場者に対して実際にデモも行っていた様です。

上のプレゼン資料の一番下の、過去発表センサとのスペック比較表は、次週以降のエントリに詳細は譲るとして、

今週最後に、上の”グローバルシャッタセンサとしての”飽和電子数のこのキヤノンのセンサの実力はどんなもんなのでしょう?

最近、丁度ソニーが(まるでキヤノンの発表にあてつけたかの様に?^^;)新規の産業用グローバルシャッタセンサのラインナップを発表しました。

その中に、画素ピッチ3.45um□、電源電圧3.3Vという、飽和電子数を比較するのには丁度良い仕様のセンサもあったのですが・・・

残念ながら、スペック表記が【mV】表記でした・・・

ほんとこういうスペックの記載単位はセンサを使う側の≒ソニーにとってお客さんになる立場の人のためにならないのでやめた方がいいと思うのですが・・・

ということで、mVでは比較不能なので、少し古いセンサになってしまいますが、

以前pointgrey社の産業用カメラ搭載センサのスペックを書いたエントリから、

ソニー製IMX250及び252という一際良い特性を示していたセンサの数字を持ってきて比較することにしました。

ちなみに上記二つのソニー製イメージセンサの画素ピッチは共に3.45um□で、

今回キヤノンが発表したセンサが、3.4um□なので、

”まあだいたい同じ土俵”と考えて良いのではないでしょうか。

で、

IMX250:10361e-

IMX252:10482e-

ということで、

single蓄積ではキヤノンの方が8100e-で小さい(≒負けている)ものの、

今回新たに開発されたと思われるmulti蓄積(実際には2回だと思われる)においては16200e-飽和が出ており、ソニーのセンサに対して1.5倍強の値ですので、

(60fpsのフレームレートで使う前提では)確かにキヤノンの主張の通り、”新開発手法は有用だ”という風に見て取れますね。

※注:ソニーのセンサの方は、何年か前のもので最新では無い

測定している組織がpointgreyとキヤノンと異なっており、双方の測定方法の違いや、測定誤差などを含んでいる

というところは勘案しなければなりませんが

今週はここまでとして、次週以降、特段のトピックニュースが出てこなければ、この続きをもう少し書きたいと思います。

(↑middle層に配置してしまうと、ロジックチップだけチップサイズを大きくするとかいう相当イレギュラーなことを行わない限り、最終的に信号データを取り出す出力パッドを配置出来ず、信号を取り出せなくなってしまう)

⇒”他方、センサ基板は受光部なので、一番上(top)に配置するしか無い”

⇒すると、後は消去法で、ロジック基板がbottomで、DRAM基板がmiddleになる

・・・という感じでしょうか?

”最終出力回路をDRAM基板に作りこめないのか?”

”最終出力回路を作りこむ場所は、DRAM基板では無くロジック基板の方が適切なのか?”

と言ったことは私はわかりません。

ただ何となくですが、DRAM自体はソニーは自分で手がけていないことから、

DRAM基板については、なるべくシンプルに本来のDRAMとしての機能に特化したチップにしたかったのかな?とかは思います。

さて、今回は、今年のISSCC2017でキヤノン発表のグローバルシャッタセンサでわかっている情報を載せてみたいと思います。

ちなみにキヤノンでグローバルシャッタセンサと言えば・・・

何故か発売延期になっていた、CINEMA EOS C700 GSモデル

及び

少し前に始めたイメージセンサの外販事業対象の3製品の内の一つ

というところが思い浮かびます。

今回のISSCC発表の方は、(後のスペック表に出てきますが、)3.4um□画素ピッチ&約5Mpix画素数センサということで、

どうやら上記後者の方のイメージセンサに関しての様子です。

↑資料のソースその1は、相変わらずImageSensorsWorldさんより

これも恐らく実際のキヤノンのプレゼン資料なのでしょうね。

”Motivation”

”開発の動機”というところでしょうか。

資料内容からすると、

”ローリングシャッターセンサは、ローリングシャッタ歪やフラッシュバンド現象が発生するので、グローバルシャッタセンサが求められている”

”画素アーキテクチャとして、赤字の素子を、従来のローリングシャッタセンサに対して画素部に追加した”

”従来のローリングシャッタセンサは、ローリングシャッタ歪に制約(ネガ)があった。

従来のグローバルシャッタセンサは、飽和、ノイズ、感度に制約(ネガ)があった

我々の開発のゴールは、それらを克服した高性能なグローバルシャッタセンサ画素を得ること”

追加素子の赤字略称はそれぞれ・・・

MEM:メモリ

OFD:オーバーフロードレイン (フォトダイオードから溢れ出した余剰電荷を捨てる排出口)

OG:オーバーフローゲート?

GS:グローバルシャッタ・・・の略でしょうか。

画素アーキテクチャ(私の表現で言うと、画素の等価回路図)は、

ソニーのグローバルシャッタセンサのタイプ(と私が予想しているもの)に近いですね、各トランジスタスイッチの名称は、それぞれの会社によって呼び方が異なる様ですが。

他には、グローバルシャッタが得意な(?)CMOSISセンサなどがありますが、CMOSISのものとは明らかに等価回路図レベルで異なるものになっています。

↑出典は同様 内容ぎっしりですね。クリックして拡大しないと見えません(^^;)

”Architecture”

直訳すると”構造”という感じでしょうか。

一番上が”Multiple-Accumulation Shutter Technique”なので、

個人的に最大の謎だった”複数蓄積シャッター技術”なるものの説明箇所。

左が従来センサ、右がキヤノンの技術・・・なのですが、如何せんImageSensorsWorldさんのoriginalを拡大してみても、若干解像度悪く・・・

とにかく読み出し速度が2倍になっていて、従来1回蓄積なところを2回蓄積している・・・というのは文字から読み取れるのですが、図が何を言いたいのかは・・・(^^;)

一番の関心事である複数回蓄積のメリットや狙いは理解出来ず(--;)

上資料左側中段”BlockDiagram”から読み取れることは、

・2画素でFD(フローティングディフュージョン:拡散容量)や画素内アンプを共有している

・出力IFは、Sub-LVDS 12bit7(←に見える)Laneが上下に一つずつ

同様に左下”Wide Aperture Light Guide”(広開口光導波路)では、

どうやら、感度アップ(維持)とPLS(寄生感度:まだ読み出し前の、前フレームの信号電荷を保存している画素内メモリ部に、遮光性能の不足等の理由による迷光のために、ノイズとして見えてしまう感度成分。低い値の方が良い性能)性能アップのために、

Light Guideと呼ぶ光導波路構造を採用した と。

お陰で特に入射角度のついた光線に対する感度downを避けることが可能になっている・・・という図に見えます。

光導波路構造については、後日part2エントリ予定の日経の別記事の図の方がわかりやすそうです。

で、上プレゼン資料の右側なのですが・・・

これもちょっと解説無しは厳しい(--;)

SS-ADCはSingle Slope ADCで、AD変換方式のことを言っており、Dual Gain Column Ampは、2つのゲインを持つ列アンプ。

で、等価回路図も列アンプの後にSS-ADCが接続されているものになっている様で、

また波形図には明らかにSS-ADCのランプ波形(三角形のもの)が記載されており、他方赤い線と青い線の列アンプの出力信号と思われるものが見えます。

が、特に赤い線の方が不自然にぐにゃっと途中で曲がる線になっており、

この2本の線がDual-Gainを意味していそうではありますが、果たしてその意味するところは・・・

結果として、文字を読むと、

この方式によって、

・ハイフレームレート (≒高速信号読み出し)

・低消費電力

の両立が図られている・・・ということの様です。

↑ImageSensorsWorldさん最後の資料

”Verification”

直訳すると”検証”

まあ、実験結果、実測確認といったところでしょうか。

右上の図からすると、

single蓄積時に8100e-(Electron:電子)の飽和電子数であるものが、

・Multi蓄積時(実際には2回蓄積の様子ですが、)に倍の16200e-の飽和電子数

になり、更には、

・長露光(8.3mSec)と短露光(84uSec)の合成によるHDR処理後には、64万e-飽和電子数相当

の画像になり、

HDR処理により+32dBのダイナミックレンジの拡大が図られましたよ

ということの様です。

その下の画像は、元資料の解像度が無いことに加え、そもそもoriginal画像を見なければwebで圧縮されたようなものを見ても正しい評価は出来ませんので、基本スルーというか本当に参考までという感じですが、

”明るいところ/暗いところ、きっちり飛ばずに/潰れずに表現できてるでしょ”

というアピールです。

しかしそれはキヤノンもわかってのことか、ISSCC当日は、来場者に対して実際にデモも行っていた様です。

上のプレゼン資料の一番下の、過去発表センサとのスペック比較表は、次週以降のエントリに詳細は譲るとして、

今週最後に、上の”グローバルシャッタセンサとしての”飽和電子数のこのキヤノンのセンサの実力はどんなもんなのでしょう?

最近、丁度ソニーが(まるでキヤノンの発表にあてつけたかの様に?^^;)新規の産業用グローバルシャッタセンサのラインナップを発表しました。

その中に、画素ピッチ3.45um□、電源電圧3.3Vという、飽和電子数を比較するのには丁度良い仕様のセンサもあったのですが・・・

残念ながら、スペック表記が【mV】表記でした・・・

ほんとこういうスペックの記載単位はセンサを使う側の≒ソニーにとってお客さんになる立場の人のためにならないのでやめた方がいいと思うのですが・・・

ということで、mVでは比較不能なので、少し古いセンサになってしまいますが、

以前pointgrey社の産業用カメラ搭載センサのスペックを書いたエントリから、

ソニー製IMX250及び252という一際良い特性を示していたセンサの数字を持ってきて比較することにしました。

ちなみに上記二つのソニー製イメージセンサの画素ピッチは共に3.45um□で、

今回キヤノンが発表したセンサが、3.4um□なので、

”まあだいたい同じ土俵”と考えて良いのではないでしょうか。

で、

IMX250:10361e-

IMX252:10482e-

ということで、

single蓄積ではキヤノンの方が8100e-で小さい(≒負けている)ものの、

今回新たに開発されたと思われるmulti蓄積(実際には2回だと思われる)においては16200e-飽和が出ており、ソニーのセンサに対して1.5倍強の値ですので、

(60fpsのフレームレートで使う前提では)確かにキヤノンの主張の通り、”新開発手法は有用だ”という風に見て取れますね。

※注:ソニーのセンサの方は、何年か前のもので最新では無い

測定している組織がpointgreyとキヤノンと異なっており、双方の測定方法の違いや、測定誤差などを含んでいる

というところは勘案しなければなりませんが

今週はここまでとして、次週以降、特段のトピックニュースが出てこなければ、この続きをもう少し書きたいと思います。

PR

ブログ内検索

カウンター

最新コメント

[03/28 hoge]

[03/26 hi-low]

[03/22 山川]

[03/18 hoge]

[03/08 hi-low]

[03/04 hoge]

[02/26 山川]

[02/26 山川]

[02/19 hoge]

[02/18 山川]

[02/05 hoge]

[02/05 hi-low]

[01/29 通りすがりです]

[01/28 FT]

[01/23 hi-low]

カテゴリー

カレンダー

最新記事

(04/22)

(04/01)

(03/25)

(03/17)

(03/11)

最古記事

プロフィール

HN:

imagerマニア

性別:

非公開