Imager マニア

デジカメ / デジタルビデオカメラ / スマホ用の撮像素子(イメージセンサ/imager/CMOSセンサ)について、マニアな情報や私見を徒然なるままに述べるBlogです(^^;)

[PR]

×

[PR]上記の広告は3ヶ月以上新規記事投稿のないブログに表示されています。新しい記事を書く事で広告が消えます。

NHK放送技術研究所公開その3 ~画素内AD搭載 3次元構造画素並列読み出しセンサ

去る17日に、VLSIシンポジウムにおいて、ソニーが4K480fps素子を発表しているはずですね。どんな内容だったのでしょうか。どこか記事にしてくれないでしょうか。気になります・・・(^^;)

さて、本エントリのサブタイトル(?)”画素内AD搭載 3次元構造画素並列読み出しセンサ”が適切かはわかりませんが(←NHKがつけた正式名称?ではありません)、

今回のエントリはこのテーマにしようと思います。前回までのNHK技研公開の続きです。

↑今年、公開されている情報の中で言えば、個人的には最も進化していたと感じたが、何故か技研公開のパンフでは一切触れられていなかった(^^;)3次元構造素子

・・・の試作チップ外観 (ケースの反射で見にくいですが^^;)

恐らく、試作チップの展示は初めてだったと思います

さて、本エントリのサブタイトル(?)”画素内AD搭載 3次元構造画素並列読み出しセンサ”が適切かはわかりませんが(←NHKがつけた正式名称?ではありません)、

今回のエントリはこのテーマにしようと思います。前回までのNHK技研公開の続きです。

↑今年、公開されている情報の中で言えば、個人的には最も進化していたと感じたが、何故か技研公開のパンフでは一切触れられていなかった(^^;)3次元構造素子

・・・の試作チップ外観 (ケースの反射で見にくいですが^^;)

恐らく、試作チップの展示は初めてだったと思います

この研究について興味おありの方は、手前味噌で恐縮すが、過去弊blogもお読みになってください。

・・・それだけだと、さすがに不親切かもしれませんので(^^;)、以下に説明は省きますが、技研で流されていたこの研究の背景部分のスライドの写真を添付します。

要約すると、

将来必要になる(とNHKが考えている)超多画素&高フレームレートな撮像素子のために、

(現行の列並列読み出しでは信号読み出しレート的に限界なので、)ウェハを複数毎貼り合わせて、画素からウェハ基板のZ(=深さ)方向に信号読み出しを行うことにより、画素並列読み出しセンサを実現するための研究・・・という感じでしょうか。

個人的には上記課題達成のために一風変わった画素内(?)ADを搭載していることがポイント(≒興味を惹かれるところ)です。

(↑最早この様な形態の場合、画素内とか画素外の定義が曖昧ですが^^;)

◆今年のこの研究の進化点その①:画素数が増えた

昨年は初めて絵(動画?)が出せて、その時の画素数が8x8=64画素でした。

が、今年は128x96=12288画素 (約1.2万画素)

これは昨年の技研公開で説明員の方が話していた通りの、いや”技研の計画通り以上の”進化ですね(^^)

(↑昨年の話では、「来年は36×24=864画素の素子を作りたい」ということでしたので)

↑1.2万画素 本モノクロセンサ で撮影された動画・・・を私が静止画で抑えたもの

もちろん、”現在のスマホの動画や静止画と比べるべくも無い”というのは一般の感想だと思いますが、去年がコレ(←写真右下あたりの”N””H””K”)だったことを思えば、相当な進歩と言っても良いように思います。

まあ、それでも既に2年前にこのくらいのモノクロ動画を出せていたNHKのもう一つの研究に比べても、まだ差があると言えば差がありますが・・・

しかし、(直接比べる対象では無いとは言え、)まだセンサ上に3層の有機膜を積層できていない有機3層撮像素子と比較すれば進捗しているとも言えると思います。

↑参考までに、撮影被写体はこんな感じ。首を左右に振っています。

光量を結構当てている様に思えるところに、このセンサの一つ課題が隠れている様な気も・・・f(^^;)

↑リアルタイムデモの撮影システム側

一つ前のblogエントリの8K240fpsセンサのカメラシステムと比較すると、”側”が即席ですね。

”シースルーにして来場者に中も見てもらおう”ということで”側をとっぱらった”・・・というよりは、恐らく”特にそんなものは作ってなかったんだけど、展示して触られて壊されたら不味いから、即席でカバーつけよう”・・・そんな感じじゃないかと予想します(^^;)

(↑いや、特に悪いことでだとは思いませんが)

ちなみに、今年の試作センサも画素ピッチは昨年までと変わらず、80um□ピッチとのこと。

デモ動画のフレームレートがいくらだったのか、聞くのを忘れてしまっていました(--;)。

恐らくmax30fpsまで程度だった様に感じました。

このセンサの採用回路アーキテクチャ(?←あとで触れます)の特徴上、階調を維持してフレームレートを稼ごうとすると、光量が必要になるため、上写真の様に入念に(?)被写体に光をあてているのだと思います。

また、冒頭写真の試作チップ≒今年の試作も、ウェハの貼り合わせ枚数は2枚とのことでした。

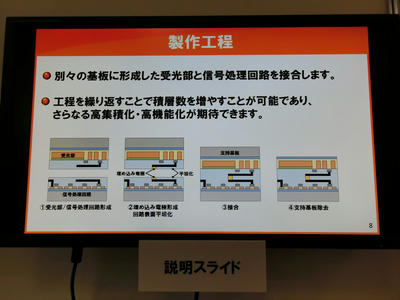

このセンサの大きな課題の内の一つの様で、ウェハ2枚貼り合わせまでは、上の”製造工程”の写真の様にお互いトランジスタなどの形成面(≒表面)同士を向き合わせて貼り合わせれば良いのですが、

3枚目以降は必ずPDでは無い側の深さ方向の回路基板(?)の支持基板を剥がしてある程度電極が届くまで薄膜化してから、次の回路形成した基板を貼り合わせなければなりません。

昨年「薄膜化のための研磨を容易にするために、SOI基板の権威である東大の平本研と組んでいる」という話を伺っていたのですが、

それでも薄膜化の研磨は難しいのか、薄膜化以外のところに大きな課題があるのか・・・その辺は聞けませんでした。

そして「来年は3層以上ウェハを貼り合わせた試作チップを期待して良いか?」との趣旨の私の質問への回答は、残念ながら

「3層目が貼り合わせられれば、4層目以降の貼り合わせの技術障壁はそれほど高くは無いが、来年には間に合わないと思う」

という回答でした。

また、今年の貼り合わせ試作チップが、

・ウェハ状態で貼り合わされたもの

か

・チップになってから貼り合わされたもの

か、聞くのを失念してしまいました。

上記も量産を本気で考えるなら重要なファクターだと思いますが、去年の感じでは「まだそこを気にする段階では無い」との技研のスタンスだった様に思いますので、

恐らく今年も原理確認優先で、チップに切り分けてからの2チップの貼り合わせによる試作ではないかと予想します。

また、ウェハ貼合わせの際の電極の形成について、

昨年までは、金電極による貼り合わせの内容がもう少しアピールされていた印象があり、

昨年のIISW2015では、NHKから主に金電極による貼り合わせが主内容の発表があったのですが、

今年の技研公開においては(既にCu電極によるウェハ貼合わせ≒積層センサが実用化されたことと関係があるのか無いのかわかりませんが、)あまりアピールされていないように感じました。

◆今年のこの研究の進化点その②:埋め込みPDになった

個人的にこのアピールを見聞きして、内心”今まで埋め込みフォトダイオードじゃなかったのかよ!”と突っ込んだことは秘密です(^^;)

なので、特にこの進化点についてのコメントはありません。

ただ、昨年までの動作原理確認の試作に埋め込みPDなど気にしているポイントでは無かったとか、この施策によって”暗電流が低減(←恐らく激減)したというのは、センサとして重要なことだと思いますので、そこは理解します。

◆今年のこの研究の進化点その③:転送スイッチ(トランジスタ)が付いた

このこと自体は、上記②と同様です。現在のCMOSイメージセンサにおいては今更な話で、しかし昨年の動作原理確認には不要であったのでついてなかった・・・ということだろうと思います。

しかしながら②と異なるのは、この施策によって、電荷検出ノード≒FD部の容量が劇的に小さくなっただろうことは、このセンサの回路アーキテクチャ(?)的には重要な進化点だと思われます。

これについては、次以降の進化点と絡めて書きたいと思います。

ちなみに「今回試作のこのチップのFD容量はいくらくらいなのですか?」との私の問いには、残念ながら「ちょっとわからない」との説明員の方の回答でした。

ちなみにこの進化点も①同様NHK技研の昨年からの計画通りです(昨年質問した際に「来年には・・・」というコメントの中にあったため)

◆今年のこの研究の進化点その④:”計測回路”≒カウンタが(画素ごとに)オンチップになった

↑今年展示されたチップの(画素)等価回路図

進化点③で書いたのは、上図で言うところの”転送ゲート”のことです。

昨年までの(画素)等価回路図はこう(←写真右下)でした。

昨年までの等価回路図にも、カウンタ≒計測回路は載っていますが、昨年の試作チップはこの計測回路はチップの外部に置いてありました(←昨年質問で確認済み)。

それが今年は画素ごとにオンチップになったということです。

これも昨年からのNHK技研の計画通りの施策です。

この”計測回路”がオンチップに出来ずに外部に置かれたままだと、それだけで最低でも1.2万画素分のセンサPAD&pinを用意しなければならず、それは間違い無く無理でアホな行為なので(^^;)、逆説的に言うと、試作チップの多画素化に必須の施策だったということの様です。

「今年のこのチップの試作で、ウェハ貼合わせのtop層とbottom層への割り振りはどうなっているのですか?」との質問に対しての回答は、

「計測回路≒カウンタがbottom側で、それ以外のトランジスタとPDは全てtop層側に配置しています」

とのことでした。

昨年の質問で、「計測回路≒カウンタは25トランジスタ程度で構成するつもり」とのお話であったので、

他の回路のトランジスタ数と比較すると、25トランジスタは多いため、

バランスと回路の区切りを考慮した結果、大枠top層とbottom層でトランジスタ数半々になるようにした結果だと予想されます。

◆今年のこの研究の進化点その⑤:④の等価回路図のインバーターの初段がコンパレータになった

個人的に今年技研公開で最も「おっ!考えたな」、もしくは「予想外」だったのがコレです(^^)

というのも、昨年もチラッと触れたのですが、この回路形式の最大の問題点の一つに、

”光量に対する分解能が異常に(?)低い(≒感度が低い?)”

というのがありました。

↑今年の説明スライドの内の一つですが、入出力特性(入ってきた光量=横軸に対してセンサ出力がどうなるか=縦軸)です。

上図で、今年のオレンジラインはまあ良いのですが、昨年までの青い”従来”のラインは、センサ特性としてまともではありません。

普通、横軸の”1lux”というのは、そこで結構もうボチボチな明るさなイメージだと思います。

しかし、昨年までのセンサでは、横軸が10^3乗=1000luxを優に上回る光量が入ってくるまでは”反応”していません(←横軸=光量が変化しても縦軸=センサ出力が変化していない)。

上図の説明では②の埋め込みPD採用による暗電流低減によってオレンジの特性に変化したかの様な印象を受けますが、

実際には③の転送ゲートを付けて、かつこの⑤の入力初段をコンパレータに変更した施策の効果の方が大きかったのではないかと、個人的に予想します。

まず、上記特性改善に最も大きな役割を果たしたのじゃないかと思っている転送ゲートをつけたことによる効果ですが、

”FD容量を小さくすることが出来、結果電荷の検出感度がその分上がった”

ということだと思います。

今年の試作チップのFD容量値は前述の通り聞けなかったのですが、昨年の転送ゲート無しのPDが直接インバーター初段入力となっている場合のPDの(いわゆる今年のFDというか電荷検出ノードの)容量値は、「200fFです」とのことでした(←昨年は質問した方が把握されている方だった)。

仮に(本当に仮に!計算のしやすさ上)今年の試作チップのFD容量値を2fF程度とすると、

昨年と今年の試作チップで1パルス=1LSBのセンサ出力をさせる=インバータを反転させるために必要な電子数(≒光量)は、今年は昨年の1/100で済むことになります。

(何故なら、検出ノードの寄生容量値が1/100であるため、V=Q/Cでいくと、同じ電子数≒電荷が容量Cに転送されてきた場合の、容量Cの電圧変化量は100倍になるため)

ちなみに、冒頭のチップ写真で、2チップ上下に並んでいる様に見えるのは、実際2チップ(≒2センサ)分焼きこまれていて(^^;)、

「FD容量を調節したものなど、実験的に2チップ分製造したからです」

とのことでした。

更に、入力初段をインバーターからコンパレータに変更した効能ですが、

”初段の回路が反転するまでに必要な電圧振幅値を小さくて済む様に追い込めるようになった”

ということかと思います。

(↑ここも自分の解釈だけで無く、それが本当に正しいのか、説明員の方に確認すれば良かったと後悔・・・--;)

昨年までの初段もインバーターの場合、インバータを構成するnMOSとpMOSの閾値が画素ごとにばらつき、実際には画素ごとのインバータの反転閾値にばらつきが生じていたと思われます。

その場合、その画素ごとの反転閾値のばらつき分、④の等価回路図の”リセット電圧”にマージンを持った≒反転するまでに必要となる電圧振幅を多めに取る(≒高めに設定する)必要があったと思われます。

(↑そうしないと≒マージンを持って高めの電圧値にしないと、下手をするとリセット電圧でも入力ノードが”high”とならずに、ずっと”Low”でリセットされっぱなしの画素が出てきてしまうため)

翻って今年の入力初段がコンパレーターの場合、

コンパレータの参照電圧(④の等価回路図のコンパレータの2入力の内”○”が入っている”-”端子側の電圧)を、同様に適切に設定することにより、

初段がインバーターの場合よりかは、反転に要するまでの電圧振幅値のマージン(?)を小さくすることが可能になるのではないかと思います。

というのは、コンパレータは初期リセットを掛けてやれば、インバータの反転閾値ばらつきほどには個体ごと(≒画素ごと)にオフセットばらつき(?)は持たないように思うからです。

↑どうでしょう?

上記コンパレータ動作(?)に関して、

及び、そもそものNHKさんが今回入力初段をインバータからコンパレータに変更した狙いに関して、

共に誤解がありそうでしたら、(出来れば”中の方”が出てきて解説して下さると嬉しいですが^^;)是非ご指摘&ご教示願います。

私が認識する限り、今年の技研の本テーマに関する進化点は以上になります。

私が興味がある点が進化したため、もしくは⑤の様に予想外の改善方法を取られたため、そう感じるのだと思うのですが、結構今まであった課題をクリアして進化した感が、個人的にはあります・・・

・・・あるのですが、しかしそれでもまだ課題は大きく多く、長い道のりなんだろうなとも感じます。

いや、こういうのは研究する側は大変で、外野で悲観的なことを述べるのは簡単だというのは世の常(?)なので、決して否定的な意味では無く、この研究のいちファン(^^;)ではあるのですが、

まず、上でも書いた様に

1) 3枚目以降の貼り合わせに苦戦中

(↑量産までの細かいことを言えば、貼り合わせに成功しても、2枚貼り合わせの現行積層センサと常に価格競争で後れを取って市場が小さい可能性大)

次に説明員の方も自覚して説明してくださいましたが、

2) この回路形式のままだと、リセットノイズが取れない

今のままだと、CMOSイメージセンサにとって必須となっているCDSが出来ないだけで無く、

そもそも、光量が多くなって ⇒ 出力パルス数が増えて ⇒ リセット回数が増えるほどに、

リセットノイズ(ランダムノイズ)が重畳されていくという恐怖の仕組みになっている

3) 2)などに対して、何か手を打とうとするとどんどん必要素子数が増えていくという悪循環

今回の⑤のインバーターからコンパレータへの変更もそうなのですが、

そもそもこのセンサの思想は、画素並列読み出しを行って高速信号読み出しを実現することにある訳です。

すると当然画素ごとに独立した読み出し回路を設ける必要があります。

そしてそれを必然”画素面積内”という(現状の画素周辺の領域や積層センサの様にbottom基板側に配置するセンサと比較すると)極めて面積(≒体積?)的に厳しい制約が存在します。

つまり、回路アーキテクチャ(?)的には簡素(≒トランジスタ数が少ない)な構成の方が好適な訳で、実際この奇抜な画素AD回路は画素内で完結させるには、

現状他のAD方式に比べて最も素子数が少なくて済む方式の様に思いますし、そこが優れた着想なのだと個人的に感じています。

なのですが、その回路アーキテクチャの弱点を補うために、⑤に加えて「来年には間に合わないと思うが、リセットノイズを除去出来る様な構成にゆくゆくはしたいと話し合っています」との説明員の方の話で、

今後も回路構成が複雑になって素子数≒ウェハ貼合わせ枚数がどんどん増える方向に行かざるを得ない雰囲気です・・・

今年までの試作チップは画素ピッチ80um□なのでまだ良いのですが、実際この技術の適用を想定している≒この技術が必要となる様な多画素センサの画素ピッチは5um□を下回ることは間違い無いと思われます。

その時に一体何枚ウェハを貼り合わせれば、必要な回路が1画素に収まりきるのか・・・?

私がこの研究の担当者であったらば目を背けたい現実です(^^;)

4) 画素ごとの信号をZ≒深さ方向にどんどんドンドン読みだしていって・・・で、最後どうやってセンサ外に出力するの?

これも質問したらば、”最終的な課題”としてNHKの方は認識されていましたが、

画素ごとに深さ方向に信号読み出しをしていって、画素ごとに出力PAD及びピンを用意する・・・というのは上記④のカウンタをオンチップ化した項に記載したのと同様ナンセンスな話です。

すると、どこかで画素ごとの信号をある程度束ねてセンサ外に出力するしかありません。

束ねるためにウェハ平面方向に信号配線を通すのは、多画素&狭ピッチセンサになるとスペース的に早々に限界がきそうです。

じゃあ配線を走らすためだけに、また何枚もウェハ積層数を増やすのか?

う~ん、個人的にはイメージが湧きませんf(^^;)

3)と4)の課題を思うと、現行の積層センサをブラッシュアップしていく方向に(究極の高速信号読み出しセンサの)最終的な解があるという危険も孕んでいるように感じます。

まあ研究というのは、必ず成功≒成就するとは限らないものなので、そういう危険があって当然と言えば当然なのですが・・・(^^;)

と、色々検討しなければならないことはあるそうですが、

「来年までにはどういう風になっていそうですか?」

との私のお決まりの質問に対しては、

「裏では色々行っていると思いますが、来年の展示にお見せ出来る内容としては、画素数向上くらいかなと思います」

とのことでした。

まあ、今年、結構急激にジャンプアップ(≒進化)してしまったので、次のジャンプアップが表に現れてくるのは、また数年後という感じになってしまうのは仕方が無いですかね。

ファンとしては、暖かい目で見て待とうかと思います(^^;)

・・・それだけだと、さすがに不親切かもしれませんので(^^;)、以下に説明は省きますが、技研で流されていたこの研究の背景部分のスライドの写真を添付します。

要約すると、

将来必要になる(とNHKが考えている)超多画素&高フレームレートな撮像素子のために、

(現行の列並列読み出しでは信号読み出しレート的に限界なので、)ウェハを複数毎貼り合わせて、画素からウェハ基板のZ(=深さ)方向に信号読み出しを行うことにより、画素並列読み出しセンサを実現するための研究・・・という感じでしょうか。

個人的には上記課題達成のために一風変わった画素内(?)ADを搭載していることがポイント(≒興味を惹かれるところ)です。

(↑最早この様な形態の場合、画素内とか画素外の定義が曖昧ですが^^;)

◆今年のこの研究の進化点その①:画素数が増えた

昨年は初めて絵(動画?)が出せて、その時の画素数が8x8=64画素でした。

が、今年は128x96=12288画素 (約1.2万画素)

これは昨年の技研公開で説明員の方が話していた通りの、いや”技研の計画通り以上の”進化ですね(^^)

(↑昨年の話では、「来年は36×24=864画素の素子を作りたい」ということでしたので)

↑1.2万画素 本モノクロセンサ で撮影された動画・・・を私が静止画で抑えたもの

もちろん、”現在のスマホの動画や静止画と比べるべくも無い”というのは一般の感想だと思いますが、去年がコレ(←写真右下あたりの”N””H””K”)だったことを思えば、相当な進歩と言っても良いように思います。

まあ、それでも既に2年前にこのくらいのモノクロ動画を出せていたNHKのもう一つの研究に比べても、まだ差があると言えば差がありますが・・・

しかし、(直接比べる対象では無いとは言え、)まだセンサ上に3層の有機膜を積層できていない有機3層撮像素子と比較すれば進捗しているとも言えると思います。

↑参考までに、撮影被写体はこんな感じ。首を左右に振っています。

光量を結構当てている様に思えるところに、このセンサの一つ課題が隠れている様な気も・・・f(^^;)

↑リアルタイムデモの撮影システム側

一つ前のblogエントリの8K240fpsセンサのカメラシステムと比較すると、”側”が即席ですね。

”シースルーにして来場者に中も見てもらおう”ということで”側をとっぱらった”・・・というよりは、恐らく”特にそんなものは作ってなかったんだけど、展示して触られて壊されたら不味いから、即席でカバーつけよう”・・・そんな感じじゃないかと予想します(^^;)

(↑いや、特に悪いことでだとは思いませんが)

ちなみに、今年の試作センサも画素ピッチは昨年までと変わらず、80um□ピッチとのこと。

デモ動画のフレームレートがいくらだったのか、聞くのを忘れてしまっていました(--;)。

恐らくmax30fpsまで程度だった様に感じました。

このセンサの採用回路アーキテクチャ(?←あとで触れます)の特徴上、階調を維持してフレームレートを稼ごうとすると、光量が必要になるため、上写真の様に入念に(?)被写体に光をあてているのだと思います。

また、冒頭写真の試作チップ≒今年の試作も、ウェハの貼り合わせ枚数は2枚とのことでした。

このセンサの大きな課題の内の一つの様で、ウェハ2枚貼り合わせまでは、上の”製造工程”の写真の様にお互いトランジスタなどの形成面(≒表面)同士を向き合わせて貼り合わせれば良いのですが、

3枚目以降は必ずPDでは無い側の深さ方向の回路基板(?)の支持基板を剥がしてある程度電極が届くまで薄膜化してから、次の回路形成した基板を貼り合わせなければなりません。

昨年「薄膜化のための研磨を容易にするために、SOI基板の権威である東大の平本研と組んでいる」という話を伺っていたのですが、

それでも薄膜化の研磨は難しいのか、薄膜化以外のところに大きな課題があるのか・・・その辺は聞けませんでした。

そして「来年は3層以上ウェハを貼り合わせた試作チップを期待して良いか?」との趣旨の私の質問への回答は、残念ながら

「3層目が貼り合わせられれば、4層目以降の貼り合わせの技術障壁はそれほど高くは無いが、来年には間に合わないと思う」

という回答でした。

また、今年の貼り合わせ試作チップが、

・ウェハ状態で貼り合わされたもの

か

・チップになってから貼り合わされたもの

か、聞くのを失念してしまいました。

上記も量産を本気で考えるなら重要なファクターだと思いますが、去年の感じでは「まだそこを気にする段階では無い」との技研のスタンスだった様に思いますので、

恐らく今年も原理確認優先で、チップに切り分けてからの2チップの貼り合わせによる試作ではないかと予想します。

また、ウェハ貼合わせの際の電極の形成について、

昨年までは、金電極による貼り合わせの内容がもう少しアピールされていた印象があり、

昨年のIISW2015では、NHKから主に金電極による貼り合わせが主内容の発表があったのですが、

今年の技研公開においては(既にCu電極によるウェハ貼合わせ≒積層センサが実用化されたことと関係があるのか無いのかわかりませんが、)あまりアピールされていないように感じました。

◆今年のこの研究の進化点その②:埋め込みPDになった

個人的にこのアピールを見聞きして、内心”今まで埋め込みフォトダイオードじゃなかったのかよ!”と突っ込んだことは秘密です(^^;)

なので、特にこの進化点についてのコメントはありません。

ただ、昨年までの動作原理確認の試作に埋め込みPDなど気にしているポイントでは無かったとか、この施策によって”暗電流が低減(←恐らく激減)したというのは、センサとして重要なことだと思いますので、そこは理解します。

◆今年のこの研究の進化点その③:転送スイッチ(トランジスタ)が付いた

このこと自体は、上記②と同様です。現在のCMOSイメージセンサにおいては今更な話で、しかし昨年の動作原理確認には不要であったのでついてなかった・・・ということだろうと思います。

しかしながら②と異なるのは、この施策によって、電荷検出ノード≒FD部の容量が劇的に小さくなっただろうことは、このセンサの回路アーキテクチャ(?)的には重要な進化点だと思われます。

これについては、次以降の進化点と絡めて書きたいと思います。

ちなみに「今回試作のこのチップのFD容量はいくらくらいなのですか?」との私の問いには、残念ながら「ちょっとわからない」との説明員の方の回答でした。

ちなみにこの進化点も①同様NHK技研の昨年からの計画通りです(昨年質問した際に「来年には・・・」というコメントの中にあったため)

◆今年のこの研究の進化点その④:”計測回路”≒カウンタが(画素ごとに)オンチップになった

↑今年展示されたチップの(画素)等価回路図

進化点③で書いたのは、上図で言うところの”転送ゲート”のことです。

昨年までの(画素)等価回路図はこう(←写真右下)でした。

昨年までの等価回路図にも、カウンタ≒計測回路は載っていますが、昨年の試作チップはこの計測回路はチップの外部に置いてありました(←昨年質問で確認済み)。

それが今年は画素ごとにオンチップになったということです。

これも昨年からのNHK技研の計画通りの施策です。

この”計測回路”がオンチップに出来ずに外部に置かれたままだと、それだけで最低でも1.2万画素分のセンサPAD&pinを用意しなければならず、それは間違い無く無理でアホな行為なので(^^;)、逆説的に言うと、試作チップの多画素化に必須の施策だったということの様です。

「今年のこのチップの試作で、ウェハ貼合わせのtop層とbottom層への割り振りはどうなっているのですか?」との質問に対しての回答は、

「計測回路≒カウンタがbottom側で、それ以外のトランジスタとPDは全てtop層側に配置しています」

とのことでした。

昨年の質問で、「計測回路≒カウンタは25トランジスタ程度で構成するつもり」とのお話であったので、

他の回路のトランジスタ数と比較すると、25トランジスタは多いため、

バランスと回路の区切りを考慮した結果、大枠top層とbottom層でトランジスタ数半々になるようにした結果だと予想されます。

◆今年のこの研究の進化点その⑤:④の等価回路図のインバーターの初段がコンパレータになった

個人的に今年技研公開で最も「おっ!考えたな」、もしくは「予想外」だったのがコレです(^^)

というのも、昨年もチラッと触れたのですが、この回路形式の最大の問題点の一つに、

”光量に対する分解能が異常に(?)低い(≒感度が低い?)”

というのがありました。

↑今年の説明スライドの内の一つですが、入出力特性(入ってきた光量=横軸に対してセンサ出力がどうなるか=縦軸)です。

上図で、今年のオレンジラインはまあ良いのですが、昨年までの青い”従来”のラインは、センサ特性としてまともではありません。

普通、横軸の”1lux”というのは、そこで結構もうボチボチな明るさなイメージだと思います。

しかし、昨年までのセンサでは、横軸が10^3乗=1000luxを優に上回る光量が入ってくるまでは”反応”していません(←横軸=光量が変化しても縦軸=センサ出力が変化していない)。

上図の説明では②の埋め込みPD採用による暗電流低減によってオレンジの特性に変化したかの様な印象を受けますが、

実際には③の転送ゲートを付けて、かつこの⑤の入力初段をコンパレータに変更した施策の効果の方が大きかったのではないかと、個人的に予想します。

まず、上記特性改善に最も大きな役割を果たしたのじゃないかと思っている転送ゲートをつけたことによる効果ですが、

”FD容量を小さくすることが出来、結果電荷の検出感度がその分上がった”

ということだと思います。

今年の試作チップのFD容量値は前述の通り聞けなかったのですが、昨年の転送ゲート無しのPDが直接インバーター初段入力となっている場合のPDの(いわゆる今年のFDというか電荷検出ノードの)容量値は、「200fFです」とのことでした(←昨年は質問した方が把握されている方だった)。

仮に(本当に仮に!計算のしやすさ上)今年の試作チップのFD容量値を2fF程度とすると、

昨年と今年の試作チップで1パルス=1LSBのセンサ出力をさせる=インバータを反転させるために必要な電子数(≒光量)は、今年は昨年の1/100で済むことになります。

(何故なら、検出ノードの寄生容量値が1/100であるため、V=Q/Cでいくと、同じ電子数≒電荷が容量Cに転送されてきた場合の、容量Cの電圧変化量は100倍になるため)

ちなみに、冒頭のチップ写真で、2チップ上下に並んでいる様に見えるのは、実際2チップ(≒2センサ)分焼きこまれていて(^^;)、

「FD容量を調節したものなど、実験的に2チップ分製造したからです」

とのことでした。

更に、入力初段をインバーターからコンパレータに変更した効能ですが、

”初段の回路が反転するまでに必要な電圧振幅値を小さくて済む様に追い込めるようになった”

ということかと思います。

(↑ここも自分の解釈だけで無く、それが本当に正しいのか、説明員の方に確認すれば良かったと後悔・・・--;)

昨年までの初段もインバーターの場合、インバータを構成するnMOSとpMOSの閾値が画素ごとにばらつき、実際には画素ごとのインバータの反転閾値にばらつきが生じていたと思われます。

その場合、その画素ごとの反転閾値のばらつき分、④の等価回路図の”リセット電圧”にマージンを持った≒反転するまでに必要となる電圧振幅を多めに取る(≒高めに設定する)必要があったと思われます。

(↑そうしないと≒マージンを持って高めの電圧値にしないと、下手をするとリセット電圧でも入力ノードが”high”とならずに、ずっと”Low”でリセットされっぱなしの画素が出てきてしまうため)

翻って今年の入力初段がコンパレーターの場合、

コンパレータの参照電圧(④の等価回路図のコンパレータの2入力の内”○”が入っている”-”端子側の電圧)を、同様に適切に設定することにより、

初段がインバーターの場合よりかは、反転に要するまでの電圧振幅値のマージン(?)を小さくすることが可能になるのではないかと思います。

というのは、コンパレータは初期リセットを掛けてやれば、インバータの反転閾値ばらつきほどには個体ごと(≒画素ごと)にオフセットばらつき(?)は持たないように思うからです。

↑どうでしょう?

上記コンパレータ動作(?)に関して、

及び、そもそものNHKさんが今回入力初段をインバータからコンパレータに変更した狙いに関して、

共に誤解がありそうでしたら、(出来れば”中の方”が出てきて解説して下さると嬉しいですが^^;)是非ご指摘&ご教示願います。

私が認識する限り、今年の技研の本テーマに関する進化点は以上になります。

私が興味がある点が進化したため、もしくは⑤の様に予想外の改善方法を取られたため、そう感じるのだと思うのですが、結構今まであった課題をクリアして進化した感が、個人的にはあります・・・

・・・あるのですが、しかしそれでもまだ課題は大きく多く、長い道のりなんだろうなとも感じます。

いや、こういうのは研究する側は大変で、外野で悲観的なことを述べるのは簡単だというのは世の常(?)なので、決して否定的な意味では無く、この研究のいちファン(^^;)ではあるのですが、

まず、上でも書いた様に

1) 3枚目以降の貼り合わせに苦戦中

(↑量産までの細かいことを言えば、貼り合わせに成功しても、2枚貼り合わせの現行積層センサと常に価格競争で後れを取って市場が小さい可能性大)

次に説明員の方も自覚して説明してくださいましたが、

2) この回路形式のままだと、リセットノイズが取れない

今のままだと、CMOSイメージセンサにとって必須となっているCDSが出来ないだけで無く、

そもそも、光量が多くなって ⇒ 出力パルス数が増えて ⇒ リセット回数が増えるほどに、

リセットノイズ(ランダムノイズ)が重畳されていくという恐怖の仕組みになっている

3) 2)などに対して、何か手を打とうとするとどんどん必要素子数が増えていくという悪循環

今回の⑤のインバーターからコンパレータへの変更もそうなのですが、

そもそもこのセンサの思想は、画素並列読み出しを行って高速信号読み出しを実現することにある訳です。

すると当然画素ごとに独立した読み出し回路を設ける必要があります。

そしてそれを必然”画素面積内”という(現状の画素周辺の領域や積層センサの様にbottom基板側に配置するセンサと比較すると)極めて面積(≒体積?)的に厳しい制約が存在します。

つまり、回路アーキテクチャ(?)的には簡素(≒トランジスタ数が少ない)な構成の方が好適な訳で、実際この奇抜な画素AD回路は画素内で完結させるには、

現状他のAD方式に比べて最も素子数が少なくて済む方式の様に思いますし、そこが優れた着想なのだと個人的に感じています。

なのですが、その回路アーキテクチャの弱点を補うために、⑤に加えて「来年には間に合わないと思うが、リセットノイズを除去出来る様な構成にゆくゆくはしたいと話し合っています」との説明員の方の話で、

今後も回路構成が複雑になって素子数≒ウェハ貼合わせ枚数がどんどん増える方向に行かざるを得ない雰囲気です・・・

今年までの試作チップは画素ピッチ80um□なのでまだ良いのですが、実際この技術の適用を想定している≒この技術が必要となる様な多画素センサの画素ピッチは5um□を下回ることは間違い無いと思われます。

その時に一体何枚ウェハを貼り合わせれば、必要な回路が1画素に収まりきるのか・・・?

私がこの研究の担当者であったらば目を背けたい現実です(^^;)

4) 画素ごとの信号をZ≒深さ方向にどんどんドンドン読みだしていって・・・で、最後どうやってセンサ外に出力するの?

これも質問したらば、”最終的な課題”としてNHKの方は認識されていましたが、

画素ごとに深さ方向に信号読み出しをしていって、画素ごとに出力PAD及びピンを用意する・・・というのは上記④のカウンタをオンチップ化した項に記載したのと同様ナンセンスな話です。

すると、どこかで画素ごとの信号をある程度束ねてセンサ外に出力するしかありません。

束ねるためにウェハ平面方向に信号配線を通すのは、多画素&狭ピッチセンサになるとスペース的に早々に限界がきそうです。

じゃあ配線を走らすためだけに、また何枚もウェハ積層数を増やすのか?

う~ん、個人的にはイメージが湧きませんf(^^;)

3)と4)の課題を思うと、現行の積層センサをブラッシュアップしていく方向に(究極の高速信号読み出しセンサの)最終的な解があるという危険も孕んでいるように感じます。

まあ研究というのは、必ず成功≒成就するとは限らないものなので、そういう危険があって当然と言えば当然なのですが・・・(^^;)

と、色々検討しなければならないことはあるそうですが、

「来年までにはどういう風になっていそうですか?」

との私のお決まりの質問に対しては、

「裏では色々行っていると思いますが、来年の展示にお見せ出来る内容としては、画素数向上くらいかなと思います」

とのことでした。

まあ、今年、結構急激にジャンプアップ(≒進化)してしまったので、次のジャンプアップが表に現れてくるのは、また数年後という感じになってしまうのは仕方が無いですかね。

ファンとしては、暖かい目で見て待とうかと思います(^^;)

PR

コメント

ブログ内検索

カウンター

最新コメント

[03/28 hoge]

[03/26 hi-low]

[03/22 山川]

[03/18 hoge]

[03/08 hi-low]

[03/04 hoge]

[02/26 山川]

[02/26 山川]

[02/19 hoge]

[02/18 山川]

[02/05 hoge]

[02/05 hi-low]

[01/29 通りすがりです]

[01/28 FT]

[01/23 hi-low]

カテゴリー

カレンダー

最新記事

(04/22)

(04/01)

(03/25)

(03/17)

(03/11)

最古記事

プロフィール

HN:

imagerマニア

性別:

非公開