Imager マニア

デジカメ / デジタルビデオカメラ / スマホ用の撮像素子(イメージセンサ/imager/CMOSセンサ)について、マニアな情報や私見を徒然なるままに述べるBlogです(^^;)

[PR]

×

[PR]上記の広告は3ヶ月以上新規記事投稿のないブログに表示されています。新しい記事を書く事で広告が消えます。

NHK技研公開2015 その2 ~画素並列信号処理3次元構造撮像デバイス ~将来の立体映像カメラの実現に向けて~

コスプレおねーさんの方は昨年くらいから急に登場するようになったような気がします。

どーもくんは最初見たときは”気持ち悪いキャラだな”と思ったのですが、何か毎年見てる内に見慣れてきて、今ではなんだか可愛く感じる様になりました(^^;)

という訳で、ひとつ”ゆるキャラランキングで投票してあげるか!”と思ったのですが、どうもどーもくんはゆるキャラランキングにはエントリーしていない様です。

そこは流石のNHKのマスコットキャラ、硬派です(^^;)

↑ 450インチ投影、フルスペック8Kスーパーハイビジョンプロジェクタ

私は撮像素子の次には表示デバイス系に興味があるのですが、

今年は撮像素子やカメラより表示デバイス系の方がやや目新しかったのでは?と思います。

NHKの言うフルスペックとは、8K、120fps、広色域(BT.2020)全てのスペックを満たしているもの。

昨年まで展示されていたプロジェクタは、800万画素×3板で、画素斜めずらし(e-shift)で擬似8Kでした。それを今年は遂に画素ずらし無しの3300万画素×3板のリアルスーパーハイビジョン。

素子サイズ1.3インチ、光源はレーザー、明暗比は5000:1。

色は確かに綺麗でしたし、通常の視聴距離で見ている限りは解像度は申し分無いように思いました。

プロジェクタの大きさ自体は50cm角くらいはあって、やはり大きいのですが(←と言っても、8Kであることを考慮すると十分小さいのですが・・・^^;)

Q.「将来はこのプロジェクタを一家に一台という風に考えられているのですか?」私

A.「いえ、そうではありません。

このプロジェクタは8Kの理解を得るために、イベント時等でその綺麗さをアピールするためのもの。実際に将来ご家庭にはフレキシブルシート型ディスプレイの方での対応を考えています。」

とのこと。

”ここから小さくするの大変そうだな~”と考えていたのですが、上記方針だと、そこまで気合入れて小型化する必要は無いということですね。

さて、ここからはやっと(^^;)撮像素子関連にいこうと思います。

今回エントリでは(ブース展示は無く、ポスター展示でしたが)以下を取り上げようと思います。

”画素並列信号処理3次元構造撮像デバイス ~将来の立体映像カメラの実現に向けて~”

この研究については、2012年から書き続けていますので、

研究の背景やこれまでの流れについてご興味おありの方は、是非昨年のエントリからお読み下さい。

ここでは割愛します。

また、今年、このテーマについては週明けから始まるオランダでのIISWで発表されることになっています。(←リンク先エントリの一番最後)

そちらでより詳しい内容が報告されると思われます。

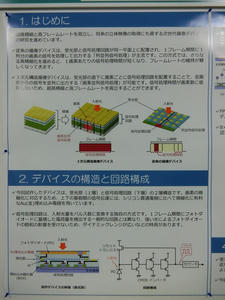

↑ 最低限の前提を簡単に

・今年も縦方向の貼り合わせウェハ枚数は2枚(=2ウェハ)

※実際には今年もウェハ単位での貼り合せは出来ておらず、ダイシング後のチップ単体の状態でのチップ同士の貼り合せにて試作したとのこと

・画素に搭載している回路は昨年エントリ通り、上の写真の右下の様なインバーターが連なってフィードバックがかかるような画素AD回路

今年も昨年通り、フォトダイオードのある1層目の基板に一緒に写真の”リセットトランジスタ”を配置。

残りの”CMOSインバーター”を2層目基板に配置という構成。

結論を書くと、今年、この研究での一番の成果は、何と言っても実際の試作チップにおいて”絵が出せた”ということだと思います。←2枚目の写真のジャギーが目立つ(^^;)”NHK”の文字がそれです。

まあ実際には

8 × 8 = 64画素

の撮像素子によるものであり、

・画素ピッチも昨年までと変わらない80um□のもの

・画素の駆動回路もオンチップでは無く外部回路からの入力

・画素パルス信号出力のカウントも、チップ外部のFPGAにおいてカウント

の状態でしたが、まあそれでも何はともあれ我々外部の人間あてには最もわかりやすい成果です(^^)。

あとは、上の写真の”まとめ”にも書いてある通り、(パルス変調の様な画素AD回路にしたお陰で)80dBのダイナミックレンジ(従来センサだとNHK曰く60dBのところを10倍のダイナミックレンジ拡張に成功)を確認できたことだとか。

そして「来年の技研公開の時にはどのように研究が進んでいる予定ですか?」私

の問いに対しての回答は、

・やはり64画素という画素数のセンサでは説得力が無い。なので来年は36×24=864画素の素子を作りたい

・そのためには、今の様なカウンタ回路と画素駆動回路をチップ外部に置く構成ではもうパッドとピン数が限界

⇒画素駆動回路をオンチップに実装。及びカウンタ回路を2層目の基板に搭載する

⇒カウンタ回路は1bitを25トランジスタで構成し(このサイトのD型フリップフロップのようなものを想定か?)16bit分載せていたい。

※25×16=400トランジスタを2層目基板に画素ごとに配置する必要があるため、来年も80um□の画素ピッチはひとまず縮める予定は無く現状のままを考えているそうです

※また、ひとまず画素数を増やすことを優先し、3層目以上のウェハ貼り合わせ枚数の増加も来年までには考えていないそうです

⇒今年も画素ごとに穴を開ける電極のアライメント精度(≒合わせズレ精度)は3um程度にまでしか追い込めていないということでした。

どうも技研としては、

「今世界にある最新装置では、300mmウェハの全域どこにおいても0.2um以内の合わせズレ以内に収めることが出来ている。最終的に量産時にはそういう装置を使いさえすれば、上記電極アライメントの問題やウェハ同士での貼り合わせの課題は解決可能」

と、考えているようで、NHK技研自体が位置合わせ精度アップや貼り合わせ枚数の増加方向の研究・検討を積極的に行うつもりは無いようでした。

その他、聞いたことや、私が「お!」と思ったことなどについて脈略無く

■(今年IISWでメインで報告されると思われる)金電極による貼り合わせについて

「最近はCu(カッパー=銅)電極でも貼り合せる動きがある様だが、金電極にこだわる理由(≒メリット)は何なのか?」私

⇒「我々は別に金にこだわっている訳では無い。ただCuだと表面が酸化してしまうのでそれを取り除く特殊な装置が必要になる。我々はその装置を持っていないので、Cuでは作れないだけ。

既存のCMOSプロセスと親和性が高いのはやはりCu電極の方。なので我々も最終的にはCu電極で製造することになると思う。

ただ、Cuが(Alと変わって)出てきた時も、最初はみな否定的だったのだ。もしかしたら今後金電極の利点が認められて主流になれれば、金電極での貼り合せ方式の方が低コストで出来るようになることもあるのでは?と思っている」

■「画素にあるADのインバーターは、何Vにまで入力が(PDからの電子の出力によって)下げられたら反転≒1パルス生成するのか?」私

⇒画素のCMOSインバーターの電源が今回の試作では1.8V。なので概略その半分の0.9Vで反転≒1パルス生成します

■「画素のFD容量≒PDが接続されているインバーターの入力ノードはどのくらいか?」私

⇒今回試作のセンサはフォトダイオードが大きくてかつ転送トランジスタも無いので、200fFとかです

上記二つの質問を私がした意図を説明員の方が察してくれて、以下の様に回答を続けて下さいました。

「このままだと、暗いところの信号は出てこないですよね?(←FD容量が大きく、かつその容量を0.9V振幅させる分の電子をPDが出力しなければならないため)

ですからゆくゆくはPDに転送トランジスタをつけてFD容量を1fFとかにして、感度を上げたいと考えています」

■「この研究を東大と共同で行っているようですが、役割分担とかはどうなっているのですか?」私

⇒東大に平本研というFD(Full Depleted:完全空乏型)-SOIの権威の先生がいらっしゃる。

3次元構造を実現するために、今いわゆる裏面照射型センサの構造だが、この貼り合わせ構造を作るには必ずウェハを薄く研磨する特殊技術が必要。

しかしそれは非常にノウハウのいることで難しい。

しかし、SOI(=Silicon On Insulator)構造のウェハを使えば、酸化膜がエッチストッパーとして存在しているため、酸化膜とシリコンの選択比が大きいエッチガスを用いれば誰でも簡単にウェハの裏面研磨を行うことが出来る。

これは今後ウェハの多層貼り合わをする上でも大変有利。

なので我々は東大の平本研と組んで研究を続けている

↑これを聞いて私は「なるほど!」と思いました(^^)

■現在1画素に(1層目と2層目の基板をつないでいる)電極は4つ

(上の2枚目のポスター写真の右上を拡大してもらえるとわかります)

回路的には上下の基板でつながなければならないのは最低2箇所=2電極あればOK

しかし、現在は製造歩留まりに余裕を出すため、同じ電気的なノードを2つづつの電極でつないでいるそうです

どーもくんは最初見たときは”気持ち悪いキャラだな”と思ったのですが、何か毎年見てる内に見慣れてきて、今ではなんだか可愛く感じる様になりました(^^;)

という訳で、ひとつ”ゆるキャラランキングで投票してあげるか!”と思ったのですが、どうもどーもくんはゆるキャラランキングにはエントリーしていない様です。

そこは流石のNHKのマスコットキャラ、硬派です(^^;)

↑ 450インチ投影、フルスペック8Kスーパーハイビジョンプロジェクタ

私は撮像素子の次には表示デバイス系に興味があるのですが、

今年は撮像素子やカメラより表示デバイス系の方がやや目新しかったのでは?と思います。

NHKの言うフルスペックとは、8K、120fps、広色域(BT.2020)全てのスペックを満たしているもの。

昨年まで展示されていたプロジェクタは、800万画素×3板で、画素斜めずらし(e-shift)で擬似8Kでした。それを今年は遂に画素ずらし無しの3300万画素×3板のリアルスーパーハイビジョン。

素子サイズ1.3インチ、光源はレーザー、明暗比は5000:1。

色は確かに綺麗でしたし、通常の視聴距離で見ている限りは解像度は申し分無いように思いました。

プロジェクタの大きさ自体は50cm角くらいはあって、やはり大きいのですが(←と言っても、8Kであることを考慮すると十分小さいのですが・・・^^;)

Q.「将来はこのプロジェクタを一家に一台という風に考えられているのですか?」私

A.「いえ、そうではありません。

このプロジェクタは8Kの理解を得るために、イベント時等でその綺麗さをアピールするためのもの。実際に将来ご家庭にはフレキシブルシート型ディスプレイの方での対応を考えています。」

とのこと。

”ここから小さくするの大変そうだな~”と考えていたのですが、上記方針だと、そこまで気合入れて小型化する必要は無いということですね。

さて、ここからはやっと(^^;)撮像素子関連にいこうと思います。

今回エントリでは(ブース展示は無く、ポスター展示でしたが)以下を取り上げようと思います。

”画素並列信号処理3次元構造撮像デバイス ~将来の立体映像カメラの実現に向けて~”

この研究については、2012年から書き続けていますので、

研究の背景やこれまでの流れについてご興味おありの方は、是非昨年のエントリからお読み下さい。

ここでは割愛します。

また、今年、このテーマについては週明けから始まるオランダでのIISWで発表されることになっています。(←リンク先エントリの一番最後)

そちらでより詳しい内容が報告されると思われます。

↑ 最低限の前提を簡単に

・今年も縦方向の貼り合わせウェハ枚数は2枚(=2ウェハ)

※実際には今年もウェハ単位での貼り合せは出来ておらず、ダイシング後のチップ単体の状態でのチップ同士の貼り合せにて試作したとのこと

・画素に搭載している回路は昨年エントリ通り、上の写真の右下の様なインバーターが連なってフィードバックがかかるような画素AD回路

今年も昨年通り、フォトダイオードのある1層目の基板に一緒に写真の”リセットトランジスタ”を配置。

残りの”CMOSインバーター”を2層目基板に配置という構成。

結論を書くと、今年、この研究での一番の成果は、何と言っても実際の試作チップにおいて”絵が出せた”ということだと思います。←2枚目の写真のジャギーが目立つ(^^;)”NHK”の文字がそれです。

まあ実際には

8 × 8 = 64画素

の撮像素子によるものであり、

・画素ピッチも昨年までと変わらない80um□のもの

・画素の駆動回路もオンチップでは無く外部回路からの入力

・画素パルス信号出力のカウントも、チップ外部のFPGAにおいてカウント

の状態でしたが、まあそれでも何はともあれ我々外部の人間あてには最もわかりやすい成果です(^^)。

あとは、上の写真の”まとめ”にも書いてある通り、(パルス変調の様な画素AD回路にしたお陰で)80dBのダイナミックレンジ(従来センサだとNHK曰く60dBのところを10倍のダイナミックレンジ拡張に成功)を確認できたことだとか。

そして「来年の技研公開の時にはどのように研究が進んでいる予定ですか?」私

の問いに対しての回答は、

・やはり64画素という画素数のセンサでは説得力が無い。なので来年は36×24=864画素の素子を作りたい

・そのためには、今の様なカウンタ回路と画素駆動回路をチップ外部に置く構成ではもうパッドとピン数が限界

⇒画素駆動回路をオンチップに実装。及びカウンタ回路を2層目の基板に搭載する

⇒カウンタ回路は1bitを25トランジスタで構成し(このサイトのD型フリップフロップのようなものを想定か?)16bit分載せていたい。

※25×16=400トランジスタを2層目基板に画素ごとに配置する必要があるため、来年も80um□の画素ピッチはひとまず縮める予定は無く現状のままを考えているそうです

※また、ひとまず画素数を増やすことを優先し、3層目以上のウェハ貼り合わせ枚数の増加も来年までには考えていないそうです

⇒今年も画素ごとに穴を開ける電極のアライメント精度(≒合わせズレ精度)は3um程度にまでしか追い込めていないということでした。

どうも技研としては、

「今世界にある最新装置では、300mmウェハの全域どこにおいても0.2um以内の合わせズレ以内に収めることが出来ている。最終的に量産時にはそういう装置を使いさえすれば、上記電極アライメントの問題やウェハ同士での貼り合わせの課題は解決可能」

と、考えているようで、NHK技研自体が位置合わせ精度アップや貼り合わせ枚数の増加方向の研究・検討を積極的に行うつもりは無いようでした。

その他、聞いたことや、私が「お!」と思ったことなどについて脈略無く

■(今年IISWでメインで報告されると思われる)金電極による貼り合わせについて

「最近はCu(カッパー=銅)電極でも貼り合せる動きがある様だが、金電極にこだわる理由(≒メリット)は何なのか?」私

⇒「我々は別に金にこだわっている訳では無い。ただCuだと表面が酸化してしまうのでそれを取り除く特殊な装置が必要になる。我々はその装置を持っていないので、Cuでは作れないだけ。

既存のCMOSプロセスと親和性が高いのはやはりCu電極の方。なので我々も最終的にはCu電極で製造することになると思う。

ただ、Cuが(Alと変わって)出てきた時も、最初はみな否定的だったのだ。もしかしたら今後金電極の利点が認められて主流になれれば、金電極での貼り合せ方式の方が低コストで出来るようになることもあるのでは?と思っている」

■「画素にあるADのインバーターは、何Vにまで入力が(PDからの電子の出力によって)下げられたら反転≒1パルス生成するのか?」私

⇒画素のCMOSインバーターの電源が今回の試作では1.8V。なので概略その半分の0.9Vで反転≒1パルス生成します

■「画素のFD容量≒PDが接続されているインバーターの入力ノードはどのくらいか?」私

⇒今回試作のセンサはフォトダイオードが大きくてかつ転送トランジスタも無いので、200fFとかです

上記二つの質問を私がした意図を説明員の方が察してくれて、以下の様に回答を続けて下さいました。

「このままだと、暗いところの信号は出てこないですよね?(←FD容量が大きく、かつその容量を0.9V振幅させる分の電子をPDが出力しなければならないため)

ですからゆくゆくはPDに転送トランジスタをつけてFD容量を1fFとかにして、感度を上げたいと考えています」

■「この研究を東大と共同で行っているようですが、役割分担とかはどうなっているのですか?」私

⇒東大に平本研というFD(Full Depleted:完全空乏型)-SOIの権威の先生がいらっしゃる。

3次元構造を実現するために、今いわゆる裏面照射型センサの構造だが、この貼り合わせ構造を作るには必ずウェハを薄く研磨する特殊技術が必要。

しかしそれは非常にノウハウのいることで難しい。

しかし、SOI(=Silicon On Insulator)構造のウェハを使えば、酸化膜がエッチストッパーとして存在しているため、酸化膜とシリコンの選択比が大きいエッチガスを用いれば誰でも簡単にウェハの裏面研磨を行うことが出来る。

これは今後ウェハの多層貼り合わをする上でも大変有利。

なので我々は東大の平本研と組んで研究を続けている

↑これを聞いて私は「なるほど!」と思いました(^^)

■現在1画素に(1層目と2層目の基板をつないでいる)電極は4つ

(上の2枚目のポスター写真の右上を拡大してもらえるとわかります)

回路的には上下の基板でつながなければならないのは最低2箇所=2電極あればOK

しかし、現在は製造歩留まりに余裕を出すため、同じ電気的なノードを2つづつの電極でつないでいるそうです

PR

コメント

ブログ内検索

カウンター

最新コメント

[03/28 hoge]

[03/26 hi-low]

[03/22 山川]

[03/18 hoge]

[03/08 hi-low]

[03/04 hoge]

[02/26 山川]

[02/26 山川]

[02/19 hoge]

[02/18 山川]

[02/05 hoge]

[02/05 hi-low]

[01/29 通りすがりです]

[01/28 FT]

[01/23 hi-low]

カテゴリー

カレンダー

最新記事

(04/22)

(04/01)

(03/25)

(03/17)

(03/11)

最古記事

プロフィール

HN:

imagerマニア

性別:

非公開