Imager マニア

デジカメ / デジタルビデオカメラ / スマホ用の撮像素子(イメージセンサ/imager/CMOSセンサ)について、マニアな情報や私見を徒然なるままに述べるBlogです(^^;)

[PR]

×

[PR]上記の広告は3ヶ月以上新規記事投稿のないブログに表示されています。新しい記事を書く事で広告が消えます。

続その3 Sony 業界初、DRAMを積層した3層構造のCMOSイメージセンサー ~TechInsightsリバースエンジニアリング編

リア充の知り合い達のSNSを眺めながらソファの上でじっと過ごしたGW f(^^;)

その締め括りがこのblogということで(^^;)

今年のNABshow2017は、どうも大きなカメラの発表は無く、各社とも良心的に(?)ファームアップ等でカメラのスペックアップを果たすという方向性だった様ですね。

他にはシネマ及び放送用のレンズの発表が豊作の年で、

その他、4Kだけでなく、現行各国の放送規格であることが多そうなFHDでのHDR(High Dynamic Range)化や、近年の流れであるVRなども継続したトピック要素だった様子です。

唯一、パナソニックから文字通り、ベールに包まれた状態の次期シネマカメラの展示があったのだとか。

これの正式発表はそう時を待たずにCINE Gear(シネギア)エキスポにて行われるそうです。

さて、本日は三度タイトル通り、ソニーの3層DRAM積層センサについて。

しかし今回はTechInsights(旧チップワークス)のblogからです。

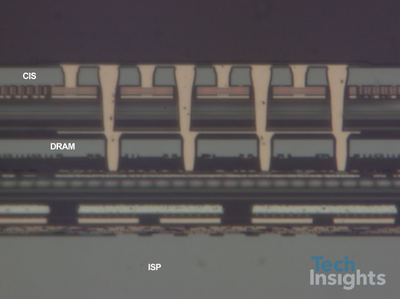

↑TechInsights解析の、ソニー3層積層センサの断面写真

かなり以前の内容と重複するところも多いため、重複箇所は割愛します。

今回TechInsightsのblogを読んでいて、個人的に「おっ」と思ったことは以下の様なところです。

その締め括りがこのblogということで(^^;)

今年のNABshow2017は、どうも大きなカメラの発表は無く、各社とも良心的に(?)ファームアップ等でカメラのスペックアップを果たすという方向性だった様ですね。

他にはシネマ及び放送用のレンズの発表が豊作の年で、

その他、4Kだけでなく、現行各国の放送規格であることが多そうなFHDでのHDR(High Dynamic Range)化や、近年の流れであるVRなども継続したトピック要素だった様子です。

唯一、パナソニックから文字通り、ベールに包まれた状態の次期シネマカメラの展示があったのだとか。

これの正式発表はそう時を待たずにCINE Gear(シネギア)エキスポにて行われるそうです。

さて、本日は三度タイトル通り、ソニーの3層DRAM積層センサについて。

しかし今回はTechInsights(旧チップワークス)のblogからです。

↑TechInsights解析の、ソニー3層積層センサの断面写真

かなり以前の内容と重複するところも多いため、重複箇所は割愛します。

今回TechInsightsのblogを読んでいて、個人的に「おっ」と思ったことは以下の様なところです。

①row driver (垂直デコーダの最終バッファ部分)はmiddleレイヤ(DRAM)die(≒チップ)に配置されている

⇒センサに要求される機能を満たし、かつ、積層されている3つのチップの面積を無駄なスペース無く同じサイズに揃えるための施策だろう

⇒そしてだからDRAMがカスタムチップということなんだろう

⇒以下は、TechInsights解析チームの予想ですが、恐らく正しいのだろうなと思います。

②DRAMチップはTechInsightsが解析したことがあるものの中で、DRAMとしては最も薄いチップだ

③恐らく、CISとISPの接続は、

では、以前の弊blog内容と重複しない箇所の中身ですが、

(以下の文章中の”我々”は、TechInsightsを指します)

・ソニーがワールドモバイルコングレスにおいて、960fpsのハイフレームレート撮影が可能なカメラを備えた、XperiaXZとXZsを発表した

・我々は早速それらのリアカメラチップの断面を見てみた

・CIS(CMOS Image Sensor)とDRAMチップはFace to backで、DRAMチップとISP(Image Signal Processor)はFace to Faceで積層されていた

・我々も多少解析したのだが、ソニーのプレスリリースとISSCCのpaperを見てみよう

・Sony used dual digital/analog converters to digitize the pixel data

↑原文まま

これ”DACが2つ搭載されていた”という風に私には読めるのですが、本当でしょうか?

digitize the pixel dataの部分を素直に読んで、ADCという風に理解すべき箇所なのでしょうか

・高速信号読み出しのための4層(4段)のADC構成

・お陰で、従来より、静止画が4倍、動画が8倍のフレームレートになった

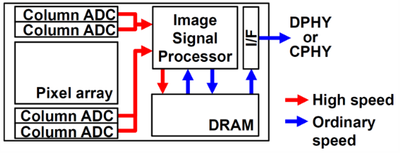

↑データフローや、信号rateなどを説明するソニーの図

しかし、既にこの辺についてはコメント欄なども含め記載済みなので割愛

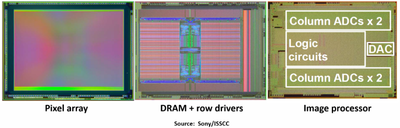

↑私の知る限り、ISSCC以外で、無料で公開されている情報では今までオープンにされていない各層のチップ写真

この写真より冒頭の

①row driver (垂直デコーダの最終バッファ部分)はmiddleレイヤ(DRAM)die(≒チップ)に配置されている

⇒センサに要求される機能を満たし、かつ、積層されている3つのチップの面積を無駄なスペース無く同じサイズに揃えるための施策だろう

⇒そしてだからDRAMがカスタムチップということなんだろう

という話が。

そして、この写真の一番右を見ると、やはりDACは一つしか載っていない様な写真の示し方に見えますが・・・?

・画素とDRAMとrow driver以外の残りの回路ブロックは、全てbottomのISPダイに載せられている

ソニーISSCC発表断面写真のスケールが正確であるならば、

・CISとDRAMチップの厚さはそれぞれ2.6um程度以下になっており、

CISチップの方は通常の裏面照射型センサと同程度の薄さだが

DRAMチップについては、我々が今まで見たことがある中では最も薄いものだ(②)

※純粋な写真の見た目では、上記記載数値ほどにはどちらも薄く無い様に見えますが、

恐らく、積層のための各die間の絶縁膜部分の厚みは除いて、純粋にシリコン部分の厚みのことを指しているのではないかと思います

・実際に我々も断面を見てみたが、ソニー発表のものと同程度の厚みであった

・また、DRAMチップに(CISから接続のために掘られてくるTSVの)ランディングパッドも見ることができた

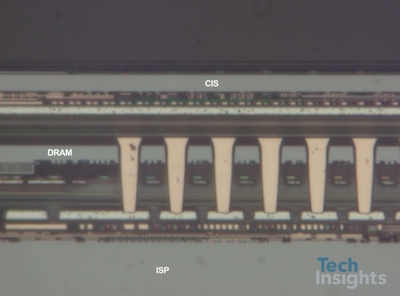

・次の疑問は、一体どうやって積層のためのTSVを作っているのか?ということだ

↑この写真の12本のTSVは全て同一ノードのものでしょうか

私にはその様に見えるのですが、この見立てが間違っていないとすると、随分と入念に(≒用心して)チップ間の電気的接続をケアしている感じですね

そして、topのセンサ画素列からmiddleチップの列ADへ信号を送るために、列で複数個所TSVが存在する理屈なはずですから、この写真の様なものがチップの至るところに(?)無数にあいているということだと思います。

・CISとDRAMのTSV接続は、良く知られたもので、初期のソニーの裏面照射積層センサで見られたもの(←一番下の写真)だった

↑DRAM-ISP間をつなぐTSVの断面写真

・我々は、チップの中で、DRAMチップをスルーして(≒突き抜けて)ダイレクトにISPチップにつながるTSVを探したが、見つけることができなかった

③恐らく、CISとISPの接続は、

⇒センサに要求される機能を満たし、かつ、積層されている3つのチップの面積を無駄なスペース無く同じサイズに揃えるための施策だろう

⇒そしてだからDRAMがカスタムチップということなんだろう

⇒以下は、TechInsights解析チームの予想ですが、恐らく正しいのだろうなと思います。

②DRAMチップはTechInsightsが解析したことがあるものの中で、DRAMとしては最も薄いチップだ

③恐らく、CISとISPの接続は、

全てのチップ積層形成後に二つのdieを貫通する穴を開けるリスクを避けるために、

DRAMのランディングPADを相互接続用として(経由して)用いているのではないかと思われる

では、以前の弊blog内容と重複しない箇所の中身ですが、

(以下の文章中の”我々”は、TechInsightsを指します)

・ソニーがワールドモバイルコングレスにおいて、960fpsのハイフレームレート撮影が可能なカメラを備えた、XperiaXZとXZsを発表した

・我々は早速それらのリアカメラチップの断面を見てみた

・CIS(CMOS Image Sensor)とDRAMチップはFace to backで、DRAMチップとISP(Image Signal Processor)はFace to Faceで積層されていた

・我々も多少解析したのだが、ソニーのプレスリリースとISSCCのpaperを見てみよう

・Sony used dual digital/analog converters to digitize the pixel data

↑原文まま

これ”DACが2つ搭載されていた”という風に私には読めるのですが、本当でしょうか?

digitize the pixel dataの部分を素直に読んで、ADCという風に理解すべき箇所なのでしょうか

・高速信号読み出しのための4層(4段)のADC構成

・お陰で、従来より、静止画が4倍、動画が8倍のフレームレートになった

↑データフローや、信号rateなどを説明するソニーの図

しかし、既にこの辺についてはコメント欄なども含め記載済みなので割愛

↑私の知る限り、ISSCC以外で、無料で公開されている情報では今までオープンにされていない各層のチップ写真

この写真より冒頭の

①row driver (垂直デコーダの最終バッファ部分)はmiddleレイヤ(DRAM)die(≒チップ)に配置されている

⇒センサに要求される機能を満たし、かつ、積層されている3つのチップの面積を無駄なスペース無く同じサイズに揃えるための施策だろう

⇒そしてだからDRAMがカスタムチップということなんだろう

という話が。

そして、この写真の一番右を見ると、やはりDACは一つしか載っていない様な写真の示し方に見えますが・・・?

・画素とDRAMとrow driver以外の残りの回路ブロックは、全てbottomのISPダイに載せられている

ソニーISSCC発表断面写真のスケールが正確であるならば、

・CISとDRAMチップの厚さはそれぞれ2.6um程度以下になっており、

CISチップの方は通常の裏面照射型センサと同程度の薄さだが

DRAMチップについては、我々が今まで見たことがある中では最も薄いものだ(②)

※純粋な写真の見た目では、上記記載数値ほどにはどちらも薄く無い様に見えますが、

恐らく、積層のための各die間の絶縁膜部分の厚みは除いて、純粋にシリコン部分の厚みのことを指しているのではないかと思います

・実際に我々も断面を見てみたが、ソニー発表のものと同程度の厚みであった

・また、DRAMチップに(CISから接続のために掘られてくるTSVの)ランディングパッドも見ることができた

・次の疑問は、一体どうやって積層のためのTSVを作っているのか?ということだ

↑この写真の12本のTSVは全て同一ノードのものでしょうか

私にはその様に見えるのですが、この見立てが間違っていないとすると、随分と入念に(≒用心して)チップ間の電気的接続をケアしている感じですね

そして、topのセンサ画素列からmiddleチップの列ADへ信号を送るために、列で複数個所TSVが存在する理屈なはずですから、この写真の様なものがチップの至るところに(?)無数にあいているということだと思います。

・CISとDRAMのTSV接続は、良く知られたもので、初期のソニーの裏面照射積層センサで見られたもの(←一番下の写真)だった

・CISのM(メタル=Cu)6層とDRAMdieのM(メタル)1層が接続されている様に見える

↑DRAM-ISP間をつなぐTSVの断面写真

・我々は、チップの中で、DRAMチップをスルーして(≒突き抜けて)ダイレクトにISPチップにつながるTSVを探したが、見つけることができなかった

③恐らく、CISとISPの接続は、

全てのチップ積層形成後に二つのdieを貫通する穴を開けるリスクを避けるために、

DRAMのランディングパッドを相互接続用として(経由して)用いているのではないかと思われる

Techinsightsとしては、もう次期iPhoneがカメラに採用する撮像素子はソニー製で決定という前提スタンスですね(^^;)

まあ私もそう思いますが

最後の文に関して言えば、個人的には”さすがにそんな短期間でドラスティックに進化したりはしないだろう”とは思ってしまいますが、

恐らくソニーのイメージセンサ部隊内部でも、Xperia用とiPhone用はチームが完全で別でしょから、

ソニーとAppleの志向の違いで、同じ世代の技術でも、性格の異なったイメージセンサができあがっているという可能性はあるのかなと思います。

・ソニーはまたスマホカメラで出来ることを増やした

そして今年後半の大きな興味、それは次期iPhoneで我々は何を見ることになるかだ

Techinsightsとしては、もう次期iPhoneがカメラに採用する撮像素子はソニー製で決定という前提スタンスですね(^^;)

まあ私もそう思いますが

最後の文に関して言えば、個人的には”さすがにそんな短期間でドラスティックに進化したりはしないだろう”とは思ってしまいますが、

恐らくソニーのイメージセンサ部隊内部でも、Xperia用とiPhone用はチームが完全で別でしょから、

ソニーとAppleの志向の違いで、同じ世代の技術でも、性格の異なったイメージセンサができあがっているという可能性はあるのかなと思います。

PR

コメント

Dual digital/analog converters

"digital/analog converters to digitize" なので、意味としてはお書きの通りに ADC と解釈すべきでしょうね。

記事筆者の書き間違いだと思います。

Re:Dual digital/analog converters

>hi-lowさん

ありがとうございます。

”digital/analog converters”

↑私が知らないだけで、この”/”が、analog-to-digital という様な意味を持たせる書き方があるのかな?

などと深読みしてました。

いずれにしても、DACを二つ持たせるメリットも良くわかりませんし、”このセンサに載っているDACは一つ”の認識でいくことにします。

ブログ内検索

カウンター

最新コメント

[03/28 hoge]

[03/26 hi-low]

[03/22 山川]

[03/18 hoge]

[03/08 hi-low]

[03/04 hoge]

[02/26 山川]

[02/26 山川]

[02/19 hoge]

[02/18 山川]

[02/05 hoge]

[02/05 hi-low]

[01/29 通りすがりです]

[01/28 FT]

[01/23 hi-low]

カテゴリー

カレンダー

最新記事

(04/22)

(04/01)

(03/25)

(03/17)

(03/11)

最古記事

プロフィール

HN:

imagerマニア

性別:

非公開