Imager マニア

デジカメ / デジタルビデオカメラ / スマホ用の撮像素子(イメージセンサ/imager/CMOSセンサ)について、マニアな情報や私見を徒然なるままに述べるBlogです(^^;)

[PR]

×

[PR]上記の広告は3ヶ月以上新規記事投稿のないブログに表示されています。新しい記事を書く事で広告が消えます。

ON Semiconductor(オンセミ) 1/2.1インチ25Mpix 逐次比較&スロープ積分型ハイブリッド列ADセンサ ~IISW2015より

先週までに引き続き、IISW2015の発表内容から。

今週は、ON Semiconductor(オンセミコンダクター)のCMOSセンサ件について。

オンセミコンダクターは、もう一件、2500万画素のセンサを発表していて、タイトルだけだと

”同じセンサ件の発表を2件に分けたのかな?”

と思っていたのですが、中身を見ると全く別物のセンサ同士でした(^^;)

↑まずはセンサ外観写真から。

どことなく、たまたまですが、先週までblogエントリしていたSamsungのNX1搭載と思われるセンサに雰囲気が似ている気がします、個人的には。

今週は、ON Semiconductor(オンセミコンダクター)のCMOSセンサ件について。

オンセミコンダクターは、もう一件、2500万画素のセンサを発表していて、タイトルだけだと

”同じセンサ件の発表を2件に分けたのかな?”

と思っていたのですが、中身を見ると全く別物のセンサ同士でした(^^;)

↑まずはセンサ外観写真から。

どことなく、たまたまですが、先週までblogエントリしていたSamsungのNX1搭載と思われるセンサに雰囲気が似ている気がします、個人的には。

最初にサラッと報告でオープンにされているこのセンサの仕様について。

①光学フォーマットサイズ:1/2.1インチ

②画素数 :2500万画素弱 (5760×4320)

③AD分解能 :12bit (逐次比較とランプ(≒シングルスロープ)のハイブリッド列AD)

④1H(≒1行)読み出し時間 :4.85uSec

⑤出力I/F :MIPI 8Lane @1Lane=1.2Gbps or HISPI 16Lane @1Lane=1.0Gbps

⑥画素ピッチ :1.1um□

⑦BSI (裏面照射型センサ)

⑧パッケージサイズ :11×11mm^2

⑨Die(≒チップ)サイズ :8.41×9.3mm^2

⑩パッケージ形態 :iBGA (Imager Ball Grid Array 121pin)

⑪画素行選択Tr無しの3トランジスタ構成

⑫3x3スキップ≒間引きもしくはbiningの4K30p及び1080p60p動画モード具備

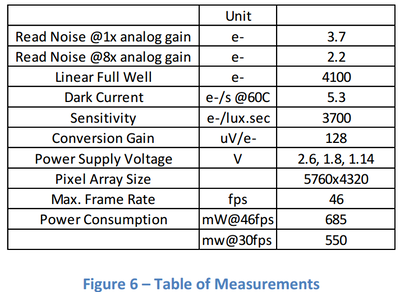

次に(若干重複しますが、)オープンにされている諸特性などについて。

↑供給電圧の項の最後の”1.14V”というのが少数第二位まできっちりと指定されるというピンポイントさっぷりが若干気になりますが、何か凄く重要なのでしょうか?(^^;)

もし”0.01Vでもズレたら正常動作を保証しない”とかだったら扱う側はビビりますね(^^;)

また、maxフレームレート46fpsの際のAD分解能は、本文記載説明によれば、10bit分解能時なので注意(?)が必要です。

また、前回の⑨でチラッと書きましたが、Read Noise(読み出しノイズ)の項は、アナログゲインが1倍と8倍時の結果が双方とも載っていて、8倍ゲイン時の方がノイズが小さくなっていますね。

これは恐らくx8倍ゲイン時のノイズの2.2電子が、ほぼアナログゲインアップ前の素子≒画素ノイズと仮定すれば(←仮定出来ないですかね?^^;)、

√(3.7^2-2.2^2)≒3.0電子が、アナログゲイン後の回路素子によるノイズ

という風に、大凡読み替えることも出来るのではないでしょうか。

今回このセンサの発表を取り上げたのは、発表内容が読みやすかったから・・・・・・

というのもあるのですが(^^;)、基本的には・・・

1)”試作(≒Sampled)となっているのだけど、スペックだけ見ると、もう製品レベルの様に思えるのだけど、これは何用を想定したセンサなのだろう?”

という好印象と好奇心が出たのと・・・

2)オンチップの列ADが逐次比較(SAR)とスロープ積分型(Ramp)のあいのこ

であったことに興味を覚えたから です。

前者1)の方はどうでしょうか?

まあ結局アナログ素子ものというのは出てくる絵を見てみるまでは、スペック表だけでは判断出来ないというのはお決まりな気はしますが(^^;)

流石に前回までのSamsungのミラーレス用のAPS-Cセンサに対しては、感度も飽和も1桁落ち(それぞれ3700e-/lux・secと4100e-)ですが、

こちらのセンサは画素ピッチが1.1um□ということで、そこは仕方の無いところかなと思います。

そして仕様面からすると、スマホ、コンパクトデジカメあたりがjust≒狙いの様に思えるものになっている(車載向けには飽和が不足していそう/マシンビジョン的にはグローバルシャッタが無い/一般監視用途にはややチップサイズが大きい?)んだけど、ONsemiのスマホ用素子というのを個人的には聞いたことが無いなと。

これは旧Aptina枠の方々の仕事でしょうか。

↑本センサのブロックダイアグラム

ここは特には。Rowデコーダ&ドライバはこのセンサも(小さいセンサですし)片側からの駆動となっていますね。

↑列回路等価回路図

列アンプ(←上図”Colamp”)が存在するあたり、Aptinaのセンサな雰囲気はあります。

そして行選択トランジスタが画素に無い3トランジスタ構成という回路図になっており、少なくともこの点は逆にNikon1に載っていたであろうAptina製センサの構成とは異なります・・・・・・

異なるのですが、よくわからないことに、このONsemiの投稿論文(?)の文章では

"The pixels are conventional 4T active pixel sensor ,but without Row Select"

(画素は典型的な4Tr構成だが、しかし行選択トランジスタは無い)となっています。

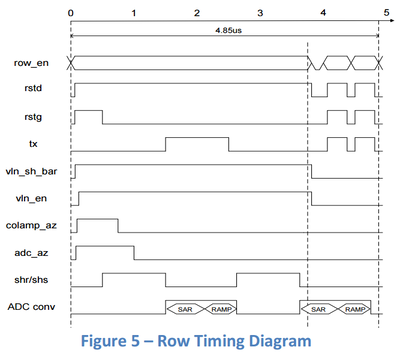

以下↓の駆動タイミングを見ても典型的な”3Tr構成の”画素駆動タイミングとなっているのですが、この文章の意味をどう捉えればよいのか私にはわかりません。

↑1行のタイミング図

そして、上図タイミング図を見ると、画素リセットMOSゲートパルスである”rstg”を1H=1行時間内でちゃんと取っていますので、Aptinaお得意の(?)ネスティングスキャン動作も行っていないセンサの様です。

しかしそれでも1行の画素信号読み出しに必要な時間は4.85uSecと、Nikon1用センサの4.58uSecとほぼ同等の時間に抑えることに成功しています。

これは現状かなり高速読み出しな部類のセンサだと思います(その結果の25Mpixのmax46fpsの仕様だと思います。そしてその際の685mWという消費電力もがんばってるんじゃないかなぁと)。

上図タイミング図の詳細は割愛したいと思いますが、等価回路図の列アンプ後の”SHR/SHS”スイッチの右の容量ノードに、AD変換前のリセットレベルもしくは(光)信号レベルをサンプルホールドすることにより、

列アンプ出力までのリセットレベルの画素から列アンプまでの読み出しと前の行の(光)信号レベルのAD変換(上図の"ADC conv"の<SAR><RAMP>)を、もしくは光信号の画素から列アンプまでの読み出しと同じ行のリセットレベルのAD変換を、並列に行うタイミングになっています。

このあたりはNikon1搭載Aptina製センサと同様の思想の様に思います(もしくは4.85uSecの1行読み出し時間を達成しようとするとmustのタイミングの様に思います)。

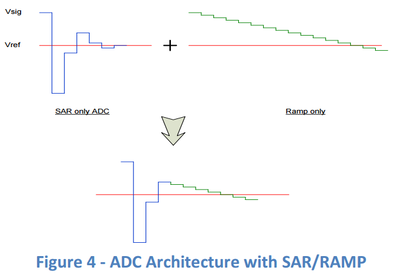

で、やっと後者2)の”オンチップの列ADが逐次比較(SAR)とスロープ積分型(Ramp)のあいのこ”の方です。

イメージセンサのオンチップ列ADで、

・シングルスロープ積分型

・逐次比較型

・サイクリック型

・ΔΣ型

の4つに続き、5つ目の候補があるとすれば、この逐次比較型とシングルスロープ積分型のハイブリッド型な気配でしょうか。

(まだ不勉強ですが、同じ5位タイくらいで、折り返し型×サイクリック型のハイブリッド型というのも研究開発レベルではあるようです)

上図上段左が逐次比較型ADイメージ、上段右がシングルスロープ積分型ADのイメージ。

そして下段が本発表オンセミセンサのハイブリッド型のイメージ。

つまり、上位bitを逐次比較で、下位bitをシングルスロープ積分型で行うというもの。

本文中では上位bit及び下位bitを以下の様に振り分けているようです。

トータル10bit分解能時:上位SAR6bit & 下位ランプ5bit

トータル12bit分解能時:上位SAR6bit & 下位ランプ7bit

ただ、上記は一例の様で、”アプリケーションのスピードとパワー(≒消費電力)の要請によって切り替える”という様な文言が付け加えられています。

そして、トータル分解能よりも常に1bit分余計(6+5=11bit)にAD変換を行うのは、”逐次比較とシングルスロープ型ADのステージ切り替え間のオフセットの補正のため”となっています。

具体的にどうオフセット補正に使うのかの記載はありませんでした。

で、結局なんでこんなしちめんどくさいハイブリッド型ADなどを考え出して採用するのかというと、本発表では以下の様にモチベーションが簡潔に書かれています(ちょっと勝手に補足していますが)。

・上位bit変換に逐次比較型を用いるのは、一重にスピードのため(特に高分解能時の)

・下位bit変換にシングルスロープ積分型を用いるのは、CDSの際の許容誤差に恩恵があるため (←つまりは乱暴に言うと低ノイズのためと言えるでしょうか)

↑チップ写真

ちょっと不鮮明ですね。わざとでしょうか?(^^;)

ひとつわかることは、画素信号はすべて写真下側の方に読み出される構成の様です(←列回路が写真下側にしか無いため)。

これは1.1umの画素ピッチセンサにおいては、片側にしか読み出さないとすると、列回路も1.1um幅でレイアウトしなければならなくなるため、レイアウト効率の低下≒チップ面積の肥大化を招きそうで、あまり得策では無いような気がするのですが、どうなのでしょうか?

それともオンチップの画像処理プロセッサみたいなものを備えていて、それを両側に設けなければならなくなるよりは片側読み出しの方がスマートということでしょうか。

最後に、それ専用の図面等は本文中に一切ありませんが、

FD boosting readout なる読み出し方法を採用しているということがかなりアピールされています。

転送ゲートとFDのカップリングを意図して増やしていて、恐らくPD信号読み出しの際の転送ゲートON=high時にFDをカップリングで高電位に振り上げて、PD信号の読み出しを補助しよう というものだと思うのですが、

表記的には”もしFDの最低電圧よりもPDのpinning電圧(?)が高くなってしまった際でも飽和電荷を増大させられる”という様なかなり怪しい(≒完全転送させられるのか疑わしい)表現になっている様な気がするので、個人的にはどうなのかな?という気がします。

また、上記以上の(例えばどうやって転送ゲートとFDのカップリングを増やしているのか?このレイアウトと駆動を行うことにより、具体的にどの程度特性が改善するのか?といった様な)詳細な情報開示はなされていませんので、これ以上この話題を取り上げるのはやめておこうと思います。

①光学フォーマットサイズ:1/2.1インチ

②画素数 :2500万画素弱 (5760×4320)

③AD分解能 :12bit (逐次比較とランプ(≒シングルスロープ)のハイブリッド列AD)

④1H(≒1行)読み出し時間 :4.85uSec

⑤出力I/F :MIPI 8Lane @1Lane=1.2Gbps or HISPI 16Lane @1Lane=1.0Gbps

⑥画素ピッチ :1.1um□

⑦BSI (裏面照射型センサ)

⑧パッケージサイズ :11×11mm^2

⑨Die(≒チップ)サイズ :8.41×9.3mm^2

⑩パッケージ形態 :iBGA (Imager Ball Grid Array 121pin)

⑪画素行選択Tr無しの3トランジスタ構成

⑫3x3スキップ≒間引きもしくはbiningの4K30p及び1080p60p動画モード具備

次に(若干重複しますが、)オープンにされている諸特性などについて。

↑供給電圧の項の最後の”1.14V”というのが少数第二位まできっちりと指定されるというピンポイントさっぷりが若干気になりますが、何か凄く重要なのでしょうか?(^^;)

もし”0.01Vでもズレたら正常動作を保証しない”とかだったら扱う側はビビりますね(^^;)

また、maxフレームレート46fpsの際のAD分解能は、本文記載説明によれば、10bit分解能時なので注意(?)が必要です。

また、前回の⑨でチラッと書きましたが、Read Noise(読み出しノイズ)の項は、アナログゲインが1倍と8倍時の結果が双方とも載っていて、8倍ゲイン時の方がノイズが小さくなっていますね。

これは恐らくx8倍ゲイン時のノイズの2.2電子が、ほぼアナログゲインアップ前の素子≒画素ノイズと仮定すれば(←仮定出来ないですかね?^^;)、

√(3.7^2-2.2^2)≒3.0電子が、アナログゲイン後の回路素子によるノイズ

という風に、大凡読み替えることも出来るのではないでしょうか。

今回このセンサの発表を取り上げたのは、発表内容が読みやすかったから・・・・・・

というのもあるのですが(^^;)、基本的には・・・

1)”試作(≒Sampled)となっているのだけど、スペックだけ見ると、もう製品レベルの様に思えるのだけど、これは何用を想定したセンサなのだろう?”

という好印象と好奇心が出たのと・・・

2)オンチップの列ADが逐次比較(SAR)とスロープ積分型(Ramp)のあいのこ

であったことに興味を覚えたから です。

前者1)の方はどうでしょうか?

まあ結局アナログ素子ものというのは出てくる絵を見てみるまでは、スペック表だけでは判断出来ないというのはお決まりな気はしますが(^^;)

流石に前回までのSamsungのミラーレス用のAPS-Cセンサに対しては、感度も飽和も1桁落ち(それぞれ3700e-/lux・secと4100e-)ですが、

こちらのセンサは画素ピッチが1.1um□ということで、そこは仕方の無いところかなと思います。

そして仕様面からすると、スマホ、コンパクトデジカメあたりがjust≒狙いの様に思えるものになっている(車載向けには飽和が不足していそう/マシンビジョン的にはグローバルシャッタが無い/一般監視用途にはややチップサイズが大きい?)んだけど、ONsemiのスマホ用素子というのを個人的には聞いたことが無いなと。

これは旧Aptina枠の方々の仕事でしょうか。

↑本センサのブロックダイアグラム

ここは特には。Rowデコーダ&ドライバはこのセンサも(小さいセンサですし)片側からの駆動となっていますね。

↑列回路等価回路図

列アンプ(←上図”Colamp”)が存在するあたり、Aptinaのセンサな雰囲気はあります。

そして行選択トランジスタが画素に無い3トランジスタ構成という回路図になっており、少なくともこの点は逆にNikon1に載っていたであろうAptina製センサの構成とは異なります・・・・・・

異なるのですが、よくわからないことに、このONsemiの投稿論文(?)の文章では

"The pixels are conventional 4T active pixel sensor ,but without Row Select"

(画素は典型的な4Tr構成だが、しかし行選択トランジスタは無い)となっています。

以下↓の駆動タイミングを見ても典型的な”3Tr構成の”画素駆動タイミングとなっているのですが、この文章の意味をどう捉えればよいのか私にはわかりません。

↑1行のタイミング図

そして、上図タイミング図を見ると、画素リセットMOSゲートパルスである”rstg”を1H=1行時間内でちゃんと取っていますので、Aptinaお得意の(?)ネスティングスキャン動作も行っていないセンサの様です。

しかしそれでも1行の画素信号読み出しに必要な時間は4.85uSecと、Nikon1用センサの4.58uSecとほぼ同等の時間に抑えることに成功しています。

これは現状かなり高速読み出しな部類のセンサだと思います(その結果の25Mpixのmax46fpsの仕様だと思います。そしてその際の685mWという消費電力もがんばってるんじゃないかなぁと)。

上図タイミング図の詳細は割愛したいと思いますが、等価回路図の列アンプ後の”SHR/SHS”スイッチの右の容量ノードに、AD変換前のリセットレベルもしくは(光)信号レベルをサンプルホールドすることにより、

列アンプ出力までのリセットレベルの画素から列アンプまでの読み出しと前の行の(光)信号レベルのAD変換(上図の"ADC conv"の<SAR><RAMP>)を、もしくは光信号の画素から列アンプまでの読み出しと同じ行のリセットレベルのAD変換を、並列に行うタイミングになっています。

このあたりはNikon1搭載Aptina製センサと同様の思想の様に思います(もしくは4.85uSecの1行読み出し時間を達成しようとするとmustのタイミングの様に思います)。

で、やっと後者2)の”オンチップの列ADが逐次比較(SAR)とスロープ積分型(Ramp)のあいのこ”の方です。

イメージセンサのオンチップ列ADで、

・シングルスロープ積分型

・逐次比較型

・サイクリック型

・ΔΣ型

の4つに続き、5つ目の候補があるとすれば、この逐次比較型とシングルスロープ積分型のハイブリッド型な気配でしょうか。

(まだ不勉強ですが、同じ5位タイくらいで、折り返し型×サイクリック型のハイブリッド型というのも研究開発レベルではあるようです)

上図上段左が逐次比較型ADイメージ、上段右がシングルスロープ積分型ADのイメージ。

そして下段が本発表オンセミセンサのハイブリッド型のイメージ。

つまり、上位bitを逐次比較で、下位bitをシングルスロープ積分型で行うというもの。

本文中では上位bit及び下位bitを以下の様に振り分けているようです。

トータル10bit分解能時:上位SAR6bit & 下位ランプ5bit

トータル12bit分解能時:上位SAR6bit & 下位ランプ7bit

ただ、上記は一例の様で、”アプリケーションのスピードとパワー(≒消費電力)の要請によって切り替える”という様な文言が付け加えられています。

そして、トータル分解能よりも常に1bit分余計(6+5=11bit)にAD変換を行うのは、”逐次比較とシングルスロープ型ADのステージ切り替え間のオフセットの補正のため”となっています。

具体的にどうオフセット補正に使うのかの記載はありませんでした。

で、結局なんでこんなしちめんどくさいハイブリッド型ADなどを考え出して採用するのかというと、本発表では以下の様にモチベーションが簡潔に書かれています(ちょっと勝手に補足していますが)。

・上位bit変換に逐次比較型を用いるのは、一重にスピードのため(特に高分解能時の)

・下位bit変換にシングルスロープ積分型を用いるのは、CDSの際の許容誤差に恩恵があるため (←つまりは乱暴に言うと低ノイズのためと言えるでしょうか)

↑チップ写真

ちょっと不鮮明ですね。わざとでしょうか?(^^;)

ひとつわかることは、画素信号はすべて写真下側の方に読み出される構成の様です(←列回路が写真下側にしか無いため)。

これは1.1umの画素ピッチセンサにおいては、片側にしか読み出さないとすると、列回路も1.1um幅でレイアウトしなければならなくなるため、レイアウト効率の低下≒チップ面積の肥大化を招きそうで、あまり得策では無いような気がするのですが、どうなのでしょうか?

それともオンチップの画像処理プロセッサみたいなものを備えていて、それを両側に設けなければならなくなるよりは片側読み出しの方がスマートということでしょうか。

最後に、それ専用の図面等は本文中に一切ありませんが、

FD boosting readout なる読み出し方法を採用しているということがかなりアピールされています。

転送ゲートとFDのカップリングを意図して増やしていて、恐らくPD信号読み出しの際の転送ゲートON=high時にFDをカップリングで高電位に振り上げて、PD信号の読み出しを補助しよう というものだと思うのですが、

表記的には”もしFDの最低電圧よりもPDのpinning電圧(?)が高くなってしまった際でも飽和電荷を増大させられる”という様なかなり怪しい(≒完全転送させられるのか疑わしい)表現になっている様な気がするので、個人的にはどうなのかな?という気がします。

また、上記以上の(例えばどうやって転送ゲートとFDのカップリングを増やしているのか?このレイアウトと駆動を行うことにより、具体的にどの程度特性が改善するのか?といった様な)詳細な情報開示はなされていませんので、これ以上この話題を取り上げるのはやめておこうと思います。

PR

コメント

ブログ内検索

カウンター

最新コメント

[03/28 hoge]

[03/26 hi-low]

[03/22 山川]

[03/18 hoge]

[03/08 hi-low]

[03/04 hoge]

[02/26 山川]

[02/26 山川]

[02/19 hoge]

[02/18 山川]

[02/05 hoge]

[02/05 hi-low]

[01/29 通りすがりです]

[01/28 FT]

[01/23 hi-low]

カテゴリー

カレンダー

最新記事

(04/22)

(04/01)

(03/25)

(03/17)

(03/11)

最古記事

プロフィール

HN:

imagerマニア

性別:

非公開