Imager マニア

デジカメ / デジタルビデオカメラ / スマホ用の撮像素子(イメージセンサ/imager/CMOSセンサ)について、マニアな情報や私見を徒然なるままに述べるBlogです(^^;)

[PR]

×

[PR]上記の広告は3ヶ月以上新規記事投稿のないブログに表示されています。新しい記事を書く事で広告が消えます。

Stacked CIS (積層型CMOS Image Sensor)の面積的効能 ~Sonyとサムスン、オムニビジョンとのチップ収量比較

積層型センサ もしくは stackedセンサと言うと、少なくとも日本ではもしかしたらFoveonの様な1画素で3原色の光を電気信号に変換可能な3層構造のセンサのことを指すと思われる方が多いかもしれません。

今回そういった意図で検索してやってこられた方には申し訳ありませんが、今回のエントリしたい”stacked CIS”はソニーが既に実用化済みのこちらの様なセンサの方です。

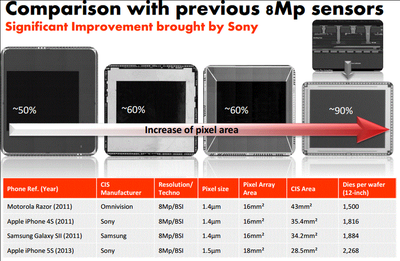

↑ ”以前の8Mpセンサとの比較 ~Sony(ソニー)がもたらした顕著な改善”

とのタイトルがついた資料

今回そういった意図で検索してやってこられた方には申し訳ありませんが、今回のエントリしたい”stacked CIS”はソニーが既に実用化済みのこちらの様なセンサの方です。

↑ ”以前の8Mpセンサとの比較 ~Sony(ソニー)がもたらした顕著な改善”

とのタイトルがついた資料

出所はこちら。←Yole developmentという会社。私は良く知らないのですが、調査会社(アナリスト≒市場分析会社)みたいなところでしょうか。

で、この情報があることを知ったのが例によっていつもお世話になっているこちらのサイトです。

今回めずらしく、前置き無しで最も言いたかったことが載っている資料を一番最初に載せました。

元記事の主張はどちらかと言うと

”TSV(シリコン貫通Via)の主用途(≒アプリケーション)の現状と今後は?”

というもので、上記写真資料は”TSV(←シリコンウェハを貫通する電気的に導通する穴)を開ける技術をイメージセンサに適用するとこんな効能がありますよ”という様なことを説明する資料になっています。

個人的にその効能(←TSVだけの恩恵では無く、むしろstaced CIS構造のメリット)がわかりやすいとても良い資料だと思います。

左が昔のソニーのセンサで、右に行くほどどうやら最近のソニーのセンサになっているようです。

写真図の中の右向き→に、”Increase of pixel area”と書かれています。

つまり、昔から今にかけて、

”ソニーのイメージセンサは、チップ面積全体に占める画素領域の割合が増えています”

ということです。

当初一番左の様に、同じ800万画素のセンサでも、チップ面積全体に占める画素領域の割合は50%しかなかったものが、(恐らく使用プロセス技術の世代が進んだことによって)中央二つの様に(画素周辺回路面積が削減されたことにより)60%に増え、更には最近は一番右の写真の様に積層型構造を取ることによって、画素領域がチップ全体に占める割合は90%にまで高まっています、と。

恐らく一番右のセンサチップは、その見た目と画素数からして、appleのiPhone5sに搭載されたチップと思われますが、90%にまで画素領域が占める面積が増えると、周辺の信号読み出し回路はほとんどtop層のシリコン基板には存在せず、その大半はbottom基板側に追いやられることになります。

そして、↑上リンク先のjpeg図の様に、top基板とbottom基板の間をつなぐのに使われているのが、TSV技術という訳です。

余談ですが、

”何故チップ面積全体に占める画素領域の割合が増えることにそんなにこだわってる(≒良いことな)のさ?”

という疑問に関しては、本質的には画素面積が占める割合が高かろうが低かろうがどうでも良いことなのですが、同じ光学フォーマットサイズのイメージセンサの場合は、上記画素領域の割合が高いチップの方が、逆に(?)チップ面積自体が小さくなることが重要です。

つまり、同じ光学フォーマットサイズのセンサであれば、センサチップ(の投影)面積が小さくなることにより、以下二つの効果が重要なのだと思われます。

1) 低コスト (で製造可能)

2) センサが組み込まれたカメラモジュール自体の投影面積もその分(以上に)小さく出来る

1)は同じ値段で売ればセンサメーカーにメリットが、2)はカメラモジュールを組み込む(例えばスマホ製造する)メーカー側の機器設計の自由度upというメリットがそれぞれもたらされることになります。

”おいおいちょっと待て!積層型センサにするってことは、bottom側の半導体基板がその分余計に必要じゃないか。bottom基板側チップの面積まで考えれば、totalのチップ面積は増えるだろうから逆にコストupなんじゃないのか!?”

上記疑問はご最もだと思います。

100%の回答にはなりませんが、少なくとも現在上記stacedセンサは、その画素ピッチの小ささもあってソニーは裏面照射型センサです。

そして裏面照射型センサの製造方法では、元々”ハンドル基板”(=支持基板)と彼らが呼ぶ”何も回路が焼きこまれていない空の”ウェハが、裏面側のフォトダイオードを露出させるために薄く研磨するためにどうしても必要でした。

つまり、どの道(ある意味)無駄に、ハンドル基板が必要だったので、”じゃあtop基板側にあった周辺回路をハンドル基板≒bottom基板側に移して焼きこんじゃえば、top基板の面積減らせるし、ハンドル基板の無駄も無くせるし、一石二鳥じゃね?”

恐らく上記がソニーの考え方です。

非常に合理的な考え方ではないでしょうか?

つまり、少なくとも基板という材料費に関して言えば、裏面照射型のセンサを製造する前提である限りは、積層型センサで1チップで2枚使ってもコストupにはなっていないと思われます。

ある意味一つのセンサで2チップ分製造する必要があるので、その歩留まり(=良品率)や純粋に回路を1チップ分余計に作りこむ製造費は、積層型センサの方が余計に掛かりますが、センサメーカーがそれでも積層型を採用しているということは、チップ面積が小さいことによるコストダウンの方が、上記コストup分を上回っているのでは無いでしょうか?

少なくともソニーは表面上は以下の様に発表しています。

「コスト面にもメリットがあるとする。CMOSセンサーは、一般的なロジックLSIに比べて設計には2倍程度の工数が掛かり投資額がかさむ問題があった。今回は画素部分と画像処理回路を別々に設計できるため投資額も抑えられる。また、新型センサーはチップサイズが小型になるため、製造コストも下がる。製造設備のキャパシティは従来の半分程度になるという。さらには、画像処理回路部分を外注することでの投資額抑制も可能だとする。」

で、やっぱり前置き説明が長くなったのですが(^^;)、私が本当にこの資料が貴重だと感じたのは実は次の部分です。

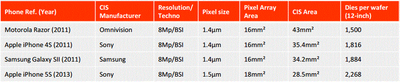

↑冒頭資料写真の下部拡大

右2列注目です。各メーカーのセンサの”チップサイズ”と12インチウェハ換算のチップの収量(=1ウェハに焼きこめるセンサチップの個数)が載っています。

恐らく解析等でチップサイズを概略0.1mm単位までは割り出して、そしてそこから求まるチップ面積から12インチウェハ面積に何個焼きこめるか見積もったのでしょうが、

通常、センサFabだけに限らず、半導体製造Fabにおいて、歩留まり、流動枚数、1ウェハの製造に必要な工程数と共にチップの収量情報は秘中の秘だと思われます。

何故なら大よそ上記情報で、そのFabの1チップ製造に掛かる費用が割り出せてしまうからです。

(半導体製造Fabにおいて、製造コストというのは競争の源泉です。エルピーダがマイクロンに買われてしまった直接の原因も単純化すれば、サムスンとマイクロンにDRAM製造コストで勝てなかったからだと思われます)

上の表の場合、センサの発売時期を無視すれば、ソニーのstacedセンサは、画素ピッチが他社より0.1um大きく、そのせいで同じ画素数センサでも画素領域が2mm^2大きいにも関わらず、チップサイズが小さいお陰で、12インチウェハ前提においては、384チップ(対Samsung比で約2割増し)も余計に多くセンサを作ることが可能になっていることになります。

同じ年の比較では無い(←ソニーだけ2013年状況。他社は2011年)ので、丸々上記差は各メーカー間で生まれていないとは思いますが、

センサチップの販売数量ベースではOmnivisionが一番ですが、売り上げ金額ベースではソニーが一番であることと、上記情報を合わせて考えると、利益額もソニーがセンサ製造メーカーの中で一番なんだろうなと容易に予想出来てしまいそうです。

逆に、上の写真の情報を信じると、2011年現在においてセンサ収量がソニーとサムスンに対して大きく劣っている(=同じ光学フォーマットにおいてチップ面積が最も大きく、収量が2割少ない)Omnivisionが、

販売数量で1位、金額で2位ということは、1チップの値付けがソニーよりも安いことを意味すると思いますが、

そうすると利益率はソニーより大きく・・・

まあ外野の私が心配することでも無いですし、全ては言う必要も無い様な気がしますね(^^;)

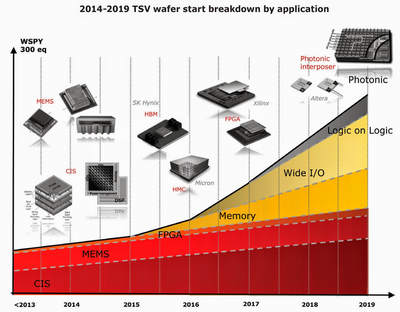

さて、元のYole development の主張を最後に以下軽く流しますと、

↑アプリケーション(用途別)TSVを用いたウェハ割合

グラフ横軸は時間(年代)ですが、最も左端が2013年です。

つまり現在においては”CIS”(CMOS Imege Sensor)が、TSVの使用用途別でNo.1とのこと。

そして今後も数年の間しばらくはNo.1のまま。

これ本当でしょうか?

多分TSV技術自体は別に元々CIS向けではなく、他の用途用に開発されたプロセス技術をセンサも使っているというだけだと思うのですが・・・?

↑”CMOS Image Sensorの革新”と題されたページ

同じく横軸は年代ですが、一番右端は、既に冒頭から記載してきたソニー製iPhone5s搭載撮像素子のものと思われる断面図ですね。

stacked CISのBototm側基板のロジック回路からと、通常裏面照射型センサのtop側の信号読み出し用の周辺回路の、双方から電気的に配線を引っ張り出すためのVia(電気的に導通している穴)を開けている図と写真。

中央はBSI(裏面照射型センサ←積層型では無い)のもの。

実装パッケージへの信号読み出しや電源供給用のワイヤがチップの上側(≒裏面側)に打たれるため、下側(表面側)に埋まった状態になっている信号読み出し&信号処理回路から電気的に配線を引っ張り出すために、やはり同様にViaを開けている図と写真。

で、一番左がFSI(表面照射型センサ)にTSVを適用した場合のもの。

表面照射型センサを通常通りパッケージングする場合には不要な例。

この一番左の例は、Wafer Level PACKageの例(←ウェハレベルパッケージとチップサイズパッケージって何が違うのでしょう?違わない?)。

センサチップ裏面に設けた半田ボールの様な端子を、センサ基板に直接半田で実装する場合、

今度は表面側にあるセンサ読み出しもしくは信号処理回路から、センサ裏面側に電気的に配線を引っ張り出す必要にかられます。

で、そのために表面側から裏面側に同様にViaを開けている図と写真。

で、originalの資料はこの後、冒頭の写真資料に移ります。

本当は、OmnivisionとSamsungの積層型センサについては少し触れようと思っていましたが、長くなってしまったので、今回はこの辺で終わりにしようと思います。

いや~しかし、ソニーはこの後この積層型センサを曲げようっていうのですから、留まるところを知りませんね~。

少し気が早いですが、センサを湾曲させた後、次にソニーが何をする気なのか非常に気になります≒興味があります(^^)

で、この情報があることを知ったのが例によっていつもお世話になっているこちらのサイトです。

今回めずらしく、前置き無しで最も言いたかったことが載っている資料を一番最初に載せました。

元記事の主張はどちらかと言うと

”TSV(シリコン貫通Via)の主用途(≒アプリケーション)の現状と今後は?”

というもので、上記写真資料は”TSV(←シリコンウェハを貫通する電気的に導通する穴)を開ける技術をイメージセンサに適用するとこんな効能がありますよ”という様なことを説明する資料になっています。

個人的にその効能(←TSVだけの恩恵では無く、むしろstaced CIS構造のメリット)がわかりやすいとても良い資料だと思います。

左が昔のソニーのセンサで、右に行くほどどうやら最近のソニーのセンサになっているようです。

写真図の中の右向き→に、”Increase of pixel area”と書かれています。

つまり、昔から今にかけて、

”ソニーのイメージセンサは、チップ面積全体に占める画素領域の割合が増えています”

ということです。

当初一番左の様に、同じ800万画素のセンサでも、チップ面積全体に占める画素領域の割合は50%しかなかったものが、(恐らく使用プロセス技術の世代が進んだことによって)中央二つの様に(画素周辺回路面積が削減されたことにより)60%に増え、更には最近は一番右の写真の様に積層型構造を取ることによって、画素領域がチップ全体に占める割合は90%にまで高まっています、と。

恐らく一番右のセンサチップは、その見た目と画素数からして、appleのiPhone5sに搭載されたチップと思われますが、90%にまで画素領域が占める面積が増えると、周辺の信号読み出し回路はほとんどtop層のシリコン基板には存在せず、その大半はbottom基板側に追いやられることになります。

そして、↑上リンク先のjpeg図の様に、top基板とbottom基板の間をつなぐのに使われているのが、TSV技術という訳です。

余談ですが、

”何故チップ面積全体に占める画素領域の割合が増えることにそんなにこだわってる(≒良いことな)のさ?”

という疑問に関しては、本質的には画素面積が占める割合が高かろうが低かろうがどうでも良いことなのですが、同じ光学フォーマットサイズのイメージセンサの場合は、上記画素領域の割合が高いチップの方が、逆に(?)チップ面積自体が小さくなることが重要です。

つまり、同じ光学フォーマットサイズのセンサであれば、センサチップ(の投影)面積が小さくなることにより、以下二つの効果が重要なのだと思われます。

1) 低コスト (で製造可能)

2) センサが組み込まれたカメラモジュール自体の投影面積もその分(以上に)小さく出来る

1)は同じ値段で売ればセンサメーカーにメリットが、2)はカメラモジュールを組み込む(例えばスマホ製造する)メーカー側の機器設計の自由度upというメリットがそれぞれもたらされることになります。

”おいおいちょっと待て!積層型センサにするってことは、bottom側の半導体基板がその分余計に必要じゃないか。bottom基板側チップの面積まで考えれば、totalのチップ面積は増えるだろうから逆にコストupなんじゃないのか!?”

上記疑問はご最もだと思います。

100%の回答にはなりませんが、少なくとも現在上記stacedセンサは、その画素ピッチの小ささもあってソニーは裏面照射型センサです。

そして裏面照射型センサの製造方法では、元々”ハンドル基板”(=支持基板)と彼らが呼ぶ”何も回路が焼きこまれていない空の”ウェハが、裏面側のフォトダイオードを露出させるために薄く研磨するためにどうしても必要でした。

つまり、どの道(ある意味)無駄に、ハンドル基板が必要だったので、”じゃあtop基板側にあった周辺回路をハンドル基板≒bottom基板側に移して焼きこんじゃえば、top基板の面積減らせるし、ハンドル基板の無駄も無くせるし、一石二鳥じゃね?”

恐らく上記がソニーの考え方です。

非常に合理的な考え方ではないでしょうか?

つまり、少なくとも基板という材料費に関して言えば、裏面照射型のセンサを製造する前提である限りは、積層型センサで1チップで2枚使ってもコストupにはなっていないと思われます。

ある意味一つのセンサで2チップ分製造する必要があるので、その歩留まり(=良品率)や純粋に回路を1チップ分余計に作りこむ製造費は、積層型センサの方が余計に掛かりますが、センサメーカーがそれでも積層型を採用しているということは、チップ面積が小さいことによるコストダウンの方が、上記コストup分を上回っているのでは無いでしょうか?

少なくともソニーは表面上は以下の様に発表しています。

「コスト面にもメリットがあるとする。CMOSセンサーは、一般的なロジックLSIに比べて設計には2倍程度の工数が掛かり投資額がかさむ問題があった。今回は画素部分と画像処理回路を別々に設計できるため投資額も抑えられる。また、新型センサーはチップサイズが小型になるため、製造コストも下がる。製造設備のキャパシティは従来の半分程度になるという。さらには、画像処理回路部分を外注することでの投資額抑制も可能だとする。」

で、やっぱり前置き説明が長くなったのですが(^^;)、私が本当にこの資料が貴重だと感じたのは実は次の部分です。

↑冒頭資料写真の下部拡大

右2列注目です。各メーカーのセンサの”チップサイズ”と12インチウェハ換算のチップの収量(=1ウェハに焼きこめるセンサチップの個数)が載っています。

恐らく解析等でチップサイズを概略0.1mm単位までは割り出して、そしてそこから求まるチップ面積から12インチウェハ面積に何個焼きこめるか見積もったのでしょうが、

通常、センサFabだけに限らず、半導体製造Fabにおいて、歩留まり、流動枚数、1ウェハの製造に必要な工程数と共にチップの収量情報は秘中の秘だと思われます。

何故なら大よそ上記情報で、そのFabの1チップ製造に掛かる費用が割り出せてしまうからです。

(半導体製造Fabにおいて、製造コストというのは競争の源泉です。エルピーダがマイクロンに買われてしまった直接の原因も単純化すれば、サムスンとマイクロンにDRAM製造コストで勝てなかったからだと思われます)

上の表の場合、センサの発売時期を無視すれば、ソニーのstacedセンサは、画素ピッチが他社より0.1um大きく、そのせいで同じ画素数センサでも画素領域が2mm^2大きいにも関わらず、チップサイズが小さいお陰で、12インチウェハ前提においては、384チップ(対Samsung比で約2割増し)も余計に多くセンサを作ることが可能になっていることになります。

同じ年の比較では無い(←ソニーだけ2013年状況。他社は2011年)ので、丸々上記差は各メーカー間で生まれていないとは思いますが、

センサチップの販売数量ベースではOmnivisionが一番ですが、売り上げ金額ベースではソニーが一番であることと、上記情報を合わせて考えると、利益額もソニーがセンサ製造メーカーの中で一番なんだろうなと容易に予想出来てしまいそうです。

逆に、上の写真の情報を信じると、2011年現在においてセンサ収量がソニーとサムスンに対して大きく劣っている(=同じ光学フォーマットにおいてチップ面積が最も大きく、収量が2割少ない)Omnivisionが、

販売数量で1位、金額で2位ということは、1チップの値付けがソニーよりも安いことを意味すると思いますが、

そうすると利益率はソニーより大きく・・・

まあ外野の私が心配することでも無いですし、全ては言う必要も無い様な気がしますね(^^;)

さて、元のYole development の主張を最後に以下軽く流しますと、

↑アプリケーション(用途別)TSVを用いたウェハ割合

グラフ横軸は時間(年代)ですが、最も左端が2013年です。

つまり現在においては”CIS”(CMOS Imege Sensor)が、TSVの使用用途別でNo.1とのこと。

そして今後も数年の間しばらくはNo.1のまま。

これ本当でしょうか?

多分TSV技術自体は別に元々CIS向けではなく、他の用途用に開発されたプロセス技術をセンサも使っているというだけだと思うのですが・・・?

↑”CMOS Image Sensorの革新”と題されたページ

同じく横軸は年代ですが、一番右端は、既に冒頭から記載してきたソニー製iPhone5s搭載撮像素子のものと思われる断面図ですね。

stacked CISのBototm側基板のロジック回路からと、通常裏面照射型センサのtop側の信号読み出し用の周辺回路の、双方から電気的に配線を引っ張り出すためのVia(電気的に導通している穴)を開けている図と写真。

中央はBSI(裏面照射型センサ←積層型では無い)のもの。

実装パッケージへの信号読み出しや電源供給用のワイヤがチップの上側(≒裏面側)に打たれるため、下側(表面側)に埋まった状態になっている信号読み出し&信号処理回路から電気的に配線を引っ張り出すために、やはり同様にViaを開けている図と写真。

で、一番左がFSI(表面照射型センサ)にTSVを適用した場合のもの。

表面照射型センサを通常通りパッケージングする場合には不要な例。

この一番左の例は、Wafer Level PACKageの例(←ウェハレベルパッケージとチップサイズパッケージって何が違うのでしょう?違わない?)。

センサチップ裏面に設けた半田ボールの様な端子を、センサ基板に直接半田で実装する場合、

今度は表面側にあるセンサ読み出しもしくは信号処理回路から、センサ裏面側に電気的に配線を引っ張り出す必要にかられます。

で、そのために表面側から裏面側に同様にViaを開けている図と写真。

で、originalの資料はこの後、冒頭の写真資料に移ります。

本当は、OmnivisionとSamsungの積層型センサについては少し触れようと思っていましたが、長くなってしまったので、今回はこの辺で終わりにしようと思います。

いや~しかし、ソニーはこの後この積層型センサを曲げようっていうのですから、留まるところを知りませんね~。

少し気が早いですが、センサを湾曲させた後、次にソニーが何をする気なのか非常に気になります≒興味があります(^^)

PR

コメント

ブログ内検索

カウンター

最新コメント

[03/28 hoge]

[03/26 hi-low]

[03/22 山川]

[03/18 hoge]

[03/08 hi-low]

[03/04 hoge]

[02/26 山川]

[02/26 山川]

[02/19 hoge]

[02/18 山川]

[02/05 hoge]

[02/05 hi-low]

[01/29 通りすがりです]

[01/28 FT]

[01/23 hi-low]

カテゴリー

カレンダー

最新記事

(04/22)

(04/01)

(03/25)

(03/17)

(03/11)

最古記事

プロフィール

HN:

imagerマニア

性別:

非公開