Imager マニア

デジカメ / デジタルビデオカメラ / スマホ用の撮像素子(イメージセンサ/imager/CMOSセンサ)について、マニアな情報や私見を徒然なるままに述べるBlogです(^^;)

[PR]

×

[PR]上記の広告は3ヶ月以上新規記事投稿のないブログに表示されています。新しい記事を書く事で広告が消えます。

ソニー 積層型裏面照射センサ(ExmorRS) ~ISSCC2013 & chipworks

ISSCC2013の第二弾。

ソニーの積層型裏面照射センサ(ExmorRS)ネタです。

(ISSCCについてはこちらのエントリの冒頭を参照ください)

以前、ソニーのスマホ搭載の積層型裏面センサの動画HDR(ハイダイナミックレンジ)機能については採りあげたことがありました。

今回は日経系の技術サイトとchipworksからの情報紹介です。

ソニーはここ2年、ISSCCで報告した技術内容を搭載したセンサを、デジタルシネマカメラ搭載撮像素子として、報告より1年以内に世に送り出してきていました。

(2011年:CINEALTAF65搭載、8K高速読み出しセンサ 2012年:CINEALTAF55搭載、グローバルシャッター機能搭載センサ)

”今回はどんな技術が出てくるのかな~?”

とimagerマニアとして楽しみにしていたところ、ちょっと肩透かしで”既に世に製品を公表済みの”センサ技術の報告でした。←いや、他の企業の先をいっているから出来ることであって、凄いことなのですが、まだ聞いたことのない内容を勝手に期待していたので(^^;)

では、上記二つのサイトよりの写真転載と共に以下より。

「」内は例によって私の勝手なプレゼン発言予測です。ご了承を。

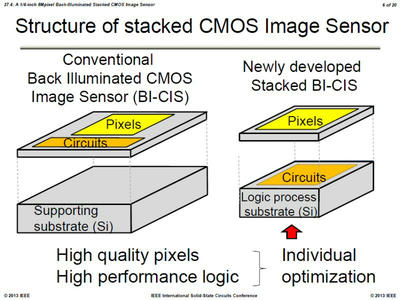

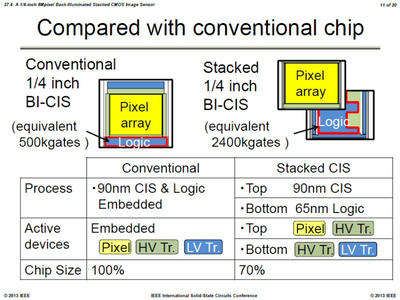

↑ 従来裏面照射センサ(左側)と今回開発した積層型(stacked)センサ(右側)との比較

「従来の裏面センサの支持基板に、Logic回路を移して集積することにより、チップ面積が70%に低減します。

また、top側の画素部とbottom側のLogic回路にそれぞれ最適なプロセスを用いることが可能というメリットがあります。」

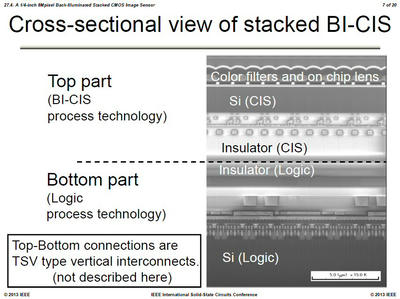

↑ Top側のCMOSイメージセンサプロセス基板(←裏面照射のために研磨して薄くなっている方)とLogic回路が載っている支持基板を積層した断面図

「積層後にtop側とbottom側をSi貫通ビアにて接続します」

※接続された箇所の断面図は、chipworksの写真を後でご紹介します。

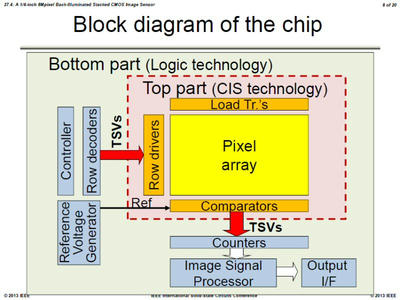

↑top側とbottom側に配置したそれぞれの回路の割り振りとTSVの位置

「”垂直のデコーダとドライバの間”

及び、”列並列に存在するコンパレータ(比較器)と列カウンタの間”でそれぞれtopとbottom基板への配置を分けて、その間をTSVで接続しました。」

「コンパレータまでを画素側のtop基板に配置することにより、(当社の低ノイズ化プロセスをtop基板側に用いることにより)より低ノイズ化が可能です」←元記事より。

※一つ前のエントリで、やはりISSCCで報告されたオリンパスの積層型CMOSを採りあげました。

上記CMOSセンサはグローバルシャッタを効率よく搭載する目的から、画素毎(←4画素ごと)にTSVを用いて積層していました。

しかし、本ソニーのセンサは画素部にはTSVは一切設けず、それぞれ垂直と水平の周辺回路部にて用いるに留めています。

これは、TSVを設ける個数が圧倒的に減ることによる歩留まり低下抑制や、そもそも画素ピッチを狭くして画素数を増やすことに大きく貢献する効率的な積層の仕方だと思います。

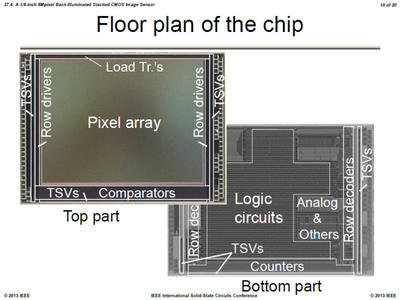

↑実際のチップのフロアプラン図

実際には、一つ前の図と異なり、垂直のデコーダーは左右に設けられていますね。

これは画素ピッチが1.12umと、比較的小さいことから、レイアウト効率を考えて、1行ごとに左右交互にデコーダとドライバを振り分けているのでしょうか。

↑従来CMOSセンサと今回の積層型センサの比較まとめ

「従来型と比較して、積層型(stacked)センサは、bottom側にLogic回路を配置することにより、Logic回路専用の(現状最適な)65nmプロセスを用いることが可能になりました。これにより、(積層型とすることでLogic回路に割り当てる面積がそもそも増えた分と合わせて、)より大きな規模のLogic回路の搭載が可能になりました。更に、Logic回路が搭載されたbottom側は外部のファウンダリに外注することも可能で、当社が常に最先端のLogicプロセスへの投資をする必要が無くなるというメリットもあります。」「また、Logic回路をbottom側へ移すことにより、チップ全体の投影面積は、従来のセンサと比較して70%程度に抑えることが可能になりました。これによりスマホなどの小型携帯機器のカメラモジュールの小型化にも貢献することが可能になります。」

※ここで気になるのは、積層型センサのbottom側にも”HV Tr”の記載がある点です。

(ここでは”HV Tr.=High Voltage transistor","LV Tr.=Low Voltage Transistor"であるはずです。)

直接発表を聞いた訳ではないので、私が意図を汲み違えている可能性が十分ありますが、ここでbottom側にはLV Tr.しかなければ、メリットを素直に頷いて聞けるのですが、HVTr.がbottom側にも存在すると、”結局Bottom側もLogic専用プロセスではなく、電源電圧の異なる混載プロセスが必要になるのじゃないか?”と思ってしまいます。

そもそも何故bottom側に”HV Tr.”が必要だったか?

2枚目の写真で言うところの”Reference Voltage Generater”,3枚目の写真で言うところの”Analog&others”がbottom側にいるからだと思われます。

本発表センサほぼそのままだと思われるソニーセンサのスペックシートを見ると、

電源電圧:digital:1.05V、Analog:2.7V

これはつまり、主にtop側が2.7VのHVTr.で、bottom側が1.05VのLVTr.であるということだと思います。

コンパレータがtop側に配置されていますので、reference voltage generator の最終出力の最大値も2.7V近くまで出力される必要があると思います。それをbottom側で作成しようとすると、1.05VのLVTr.だけでは難しく、結局参照電圧生成器にHVTr.を使用せざると得なくなった。また、もしかししたら”analog&others”の中にtop側で使う1.05V以上の中間電源を生成しているとすると、そのためにもHVTr.は必要になりそうです(←回路によっては中間電源等必要でない可能性もあるので、今回のチップにこの様な中間電源をbottom側で作成しているかは不明ですが)。

では何故”Analog&others”をtop側にもっていかなかったのか?

単純にチップの投影面積の縮小を優先したのでしょうか。

私にはそれぐらいしか思いつきません。

3枚目の写真でanalog&othersはそれなりの面積を持っています。ですので確かにそれをtop側に持っていってしまうと、それなりに面積が増えて、今回の技術のメリットを多少スポイルする方向になってしまいそうです。

まあ、オリジナルのスペックシートを見るとI/Fは1.8~2.9Vとなっており、ここでそもそもHVTr.が必要になりそうです。

このチップ構成ですと、どう考えても出力はbottom側からされるでしょうから、どちらにしてもbottom側にHVTr.が必要になるので、面積効率からanalog&othersもbottom側にするというのは理解できる話だと思います。

ただ、私が理解できないのはI/F電圧はこのチップの都合からすれば、LVTr.でまかなえる程度の低い電圧値でも問題ないように思います。この1.8~2.9Vというのは、スマホなどのシステム設計側の従来製品とのコンパチ性とかの要望でこの様な電圧にしているのでしょうか?←それとも私の知らない出力I/Fの規格等の問題で1.8~2.9Vにせざるを得ないのでしょうか?

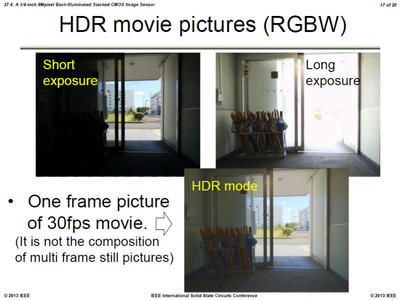

↑本センサチップ単体で画像処理可能になった機能の内の一つの例の紹介。

動画でのHDR(←ハイダイナミックレンジ)機能で撮られた実際の絵

「bottom側に配置した豊富なLogic回路によって、センサチップ単体で実現可能な画像処理の1例として、動画時のHDR機能があります。」「絵を見ていただければ、十分な効果が見て取れると思います。ここで注意していただきたいのは、この動画の絵は”複数枚の絵の合成”によって実現しているわけではなく、あくまで1枚絵で実現しているところです。ですので動画フレームレートも30fpsと、通常の動画モードから落ちません。」

※この動画時のHDRモードの実現方法はこれだと思われます。

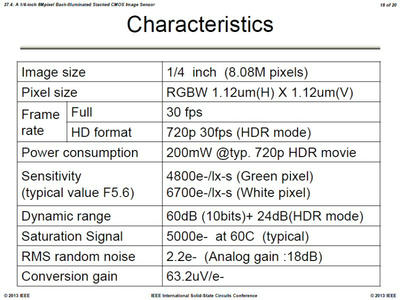

↑本センサの特性まとめ

※見たとおりですが、

まずRGBW画素(white画素)を採用しているところが特徴でしょうか。もちろん感度upを狙ってのことだと思います。

そして画素ピッチの1.12um□。

これは業界最小クラスの画素ピッチです。

また、フレームレートの”Full”が800万画素を指すとすると、スマホとかに搭載されるセンサであることを考えると、相当高速連写可能な部類ではないでしょうか。

感度の値は、普段あまりソニーも含め他社が電子数表示することが少ないので、特性値として凄いのか普通なのかいまひとつ私にはピンときません。しかし、この極小画素ピッチでの話なので恐らく凄い部類なのであろうと思います。

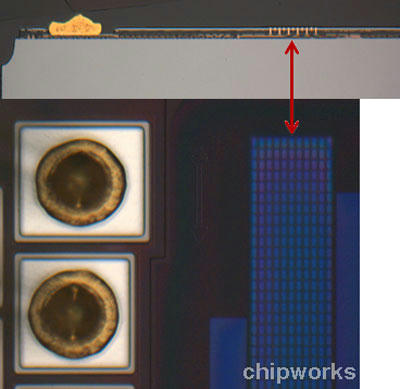

そして以下はchipworksからの写真になります。

↑ 実際にソニーのスマホから取り出したカメラモジュール

”SiP(=System In Package) Here”の文字が(^^;)。

↑ 恐らく、垂直のデコーダ部側のTSV部

chipworksによると、TSVのピッチは6um。

前回のオリンパスの積層型センサが画素部で8umピッチ。

現状の積層型センサの現実的なところはこのくらいのピッチなのでしょう。

TSV部が1列ではなく11列程度になっています。

これは画素ピッチが1.12umでTSVのピッチが6um(←写真では縦のピッチは更に倍の12um程度になっているように見えますが?)。

1列で並べていては必要な穴の数が確保できないために、列数を増やしているのでしょう。

また、どうでも良い話ですが、左側に移っているボンディングパッドの大きさが異なるのが気になりますね。何か意味あるのでしょうか?(^^;)

ソニーの積層型裏面照射センサ(ExmorRS)ネタです。

(ISSCCについてはこちらのエントリの冒頭を参照ください)

以前、ソニーのスマホ搭載の積層型裏面センサの動画HDR(ハイダイナミックレンジ)機能については採りあげたことがありました。

今回は日経系の技術サイトとchipworksからの情報紹介です。

ソニーはここ2年、ISSCCで報告した技術内容を搭載したセンサを、デジタルシネマカメラ搭載撮像素子として、報告より1年以内に世に送り出してきていました。

(2011年:CINEALTAF65搭載、8K高速読み出しセンサ 2012年:CINEALTAF55搭載、グローバルシャッター機能搭載センサ)

”今回はどんな技術が出てくるのかな~?”

とimagerマニアとして楽しみにしていたところ、ちょっと肩透かしで”既に世に製品を公表済みの”センサ技術の報告でした。←いや、他の企業の先をいっているから出来ることであって、凄いことなのですが、まだ聞いたことのない内容を勝手に期待していたので(^^;)

では、上記二つのサイトよりの写真転載と共に以下より。

「」内は例によって私の勝手なプレゼン発言予測です。ご了承を。

↑ 従来裏面照射センサ(左側)と今回開発した積層型(stacked)センサ(右側)との比較

「従来の裏面センサの支持基板に、Logic回路を移して集積することにより、チップ面積が70%に低減します。

また、top側の画素部とbottom側のLogic回路にそれぞれ最適なプロセスを用いることが可能というメリットがあります。」

↑ Top側のCMOSイメージセンサプロセス基板(←裏面照射のために研磨して薄くなっている方)とLogic回路が載っている支持基板を積層した断面図

「積層後にtop側とbottom側をSi貫通ビアにて接続します」

※接続された箇所の断面図は、chipworksの写真を後でご紹介します。

↑top側とbottom側に配置したそれぞれの回路の割り振りとTSVの位置

「”垂直のデコーダとドライバの間”

及び、”列並列に存在するコンパレータ(比較器)と列カウンタの間”でそれぞれtopとbottom基板への配置を分けて、その間をTSVで接続しました。」

「コンパレータまでを画素側のtop基板に配置することにより、(当社の低ノイズ化プロセスをtop基板側に用いることにより)より低ノイズ化が可能です」←元記事より。

※一つ前のエントリで、やはりISSCCで報告されたオリンパスの積層型CMOSを採りあげました。

上記CMOSセンサはグローバルシャッタを効率よく搭載する目的から、画素毎(←4画素ごと)にTSVを用いて積層していました。

しかし、本ソニーのセンサは画素部にはTSVは一切設けず、それぞれ垂直と水平の周辺回路部にて用いるに留めています。

これは、TSVを設ける個数が圧倒的に減ることによる歩留まり低下抑制や、そもそも画素ピッチを狭くして画素数を増やすことに大きく貢献する効率的な積層の仕方だと思います。

↑実際のチップのフロアプラン図

実際には、一つ前の図と異なり、垂直のデコーダーは左右に設けられていますね。

これは画素ピッチが1.12umと、比較的小さいことから、レイアウト効率を考えて、1行ごとに左右交互にデコーダとドライバを振り分けているのでしょうか。

↑従来CMOSセンサと今回の積層型センサの比較まとめ

「従来型と比較して、積層型(stacked)センサは、bottom側にLogic回路を配置することにより、Logic回路専用の(現状最適な)65nmプロセスを用いることが可能になりました。これにより、(積層型とすることでLogic回路に割り当てる面積がそもそも増えた分と合わせて、)より大きな規模のLogic回路の搭載が可能になりました。更に、Logic回路が搭載されたbottom側は外部のファウンダリに外注することも可能で、当社が常に最先端のLogicプロセスへの投資をする必要が無くなるというメリットもあります。」「また、Logic回路をbottom側へ移すことにより、チップ全体の投影面積は、従来のセンサと比較して70%程度に抑えることが可能になりました。これによりスマホなどの小型携帯機器のカメラモジュールの小型化にも貢献することが可能になります。」

※ここで気になるのは、積層型センサのbottom側にも”HV Tr”の記載がある点です。

(ここでは”HV Tr.=High Voltage transistor","LV Tr.=Low Voltage Transistor"であるはずです。)

直接発表を聞いた訳ではないので、私が意図を汲み違えている可能性が十分ありますが、ここでbottom側にはLV Tr.しかなければ、メリットを素直に頷いて聞けるのですが、HVTr.がbottom側にも存在すると、”結局Bottom側もLogic専用プロセスではなく、電源電圧の異なる混載プロセスが必要になるのじゃないか?”と思ってしまいます。

そもそも何故bottom側に”HV Tr.”が必要だったか?

2枚目の写真で言うところの”Reference Voltage Generater”,3枚目の写真で言うところの”Analog&others”がbottom側にいるからだと思われます。

本発表センサほぼそのままだと思われるソニーセンサのスペックシートを見ると、

電源電圧:digital:1.05V、Analog:2.7V

これはつまり、主にtop側が2.7VのHVTr.で、bottom側が1.05VのLVTr.であるということだと思います。

コンパレータがtop側に配置されていますので、reference voltage generator の最終出力の最大値も2.7V近くまで出力される必要があると思います。それをbottom側で作成しようとすると、1.05VのLVTr.だけでは難しく、結局参照電圧生成器にHVTr.を使用せざると得なくなった。また、もしかししたら”analog&others”の中にtop側で使う1.05V以上の中間電源を生成しているとすると、そのためにもHVTr.は必要になりそうです(←回路によっては中間電源等必要でない可能性もあるので、今回のチップにこの様な中間電源をbottom側で作成しているかは不明ですが)。

では何故”Analog&others”をtop側にもっていかなかったのか?

単純にチップの投影面積の縮小を優先したのでしょうか。

私にはそれぐらいしか思いつきません。

3枚目の写真でanalog&othersはそれなりの面積を持っています。ですので確かにそれをtop側に持っていってしまうと、それなりに面積が増えて、今回の技術のメリットを多少スポイルする方向になってしまいそうです。

まあ、オリジナルのスペックシートを見るとI/Fは1.8~2.9Vとなっており、ここでそもそもHVTr.が必要になりそうです。

このチップ構成ですと、どう考えても出力はbottom側からされるでしょうから、どちらにしてもbottom側にHVTr.が必要になるので、面積効率からanalog&othersもbottom側にするというのは理解できる話だと思います。

ただ、私が理解できないのはI/F電圧はこのチップの都合からすれば、LVTr.でまかなえる程度の低い電圧値でも問題ないように思います。この1.8~2.9Vというのは、スマホなどのシステム設計側の従来製品とのコンパチ性とかの要望でこの様な電圧にしているのでしょうか?←それとも私の知らない出力I/Fの規格等の問題で1.8~2.9Vにせざるを得ないのでしょうか?

↑本センサチップ単体で画像処理可能になった機能の内の一つの例の紹介。

動画でのHDR(←ハイダイナミックレンジ)機能で撮られた実際の絵

「bottom側に配置した豊富なLogic回路によって、センサチップ単体で実現可能な画像処理の1例として、動画時のHDR機能があります。」「絵を見ていただければ、十分な効果が見て取れると思います。ここで注意していただきたいのは、この動画の絵は”複数枚の絵の合成”によって実現しているわけではなく、あくまで1枚絵で実現しているところです。ですので動画フレームレートも30fpsと、通常の動画モードから落ちません。」

※この動画時のHDRモードの実現方法はこれだと思われます。

↑本センサの特性まとめ

※見たとおりですが、

まずRGBW画素(white画素)を採用しているところが特徴でしょうか。もちろん感度upを狙ってのことだと思います。

そして画素ピッチの1.12um□。

これは業界最小クラスの画素ピッチです。

また、フレームレートの”Full”が800万画素を指すとすると、スマホとかに搭載されるセンサであることを考えると、相当高速連写可能な部類ではないでしょうか。

感度の値は、普段あまりソニーも含め他社が電子数表示することが少ないので、特性値として凄いのか普通なのかいまひとつ私にはピンときません。しかし、この極小画素ピッチでの話なので恐らく凄い部類なのであろうと思います。

そして以下はchipworksからの写真になります。

↑ 実際にソニーのスマホから取り出したカメラモジュール

”SiP(=System In Package) Here”の文字が(^^;)。

↑ 恐らく、垂直のデコーダ部側のTSV部

chipworksによると、TSVのピッチは6um。

前回のオリンパスの積層型センサが画素部で8umピッチ。

現状の積層型センサの現実的なところはこのくらいのピッチなのでしょう。

TSV部が1列ではなく11列程度になっています。

これは画素ピッチが1.12umでTSVのピッチが6um(←写真では縦のピッチは更に倍の12um程度になっているように見えますが?)。

1列で並べていては必要な穴の数が確保できないために、列数を増やしているのでしょう。

また、どうでも良い話ですが、左側に移っているボンディングパッドの大きさが異なるのが気になりますね。何か意味あるのでしょうか?(^^;)

PR

コメント

ブログ内検索

カウンター

最新コメント

[03/28 hoge]

[03/26 hi-low]

[03/22 山川]

[03/18 hoge]

[03/08 hi-low]

[03/04 hoge]

[02/26 山川]

[02/26 山川]

[02/19 hoge]

[02/18 山川]

[02/05 hoge]

[02/05 hi-low]

[01/29 通りすがりです]

[01/28 FT]

[01/23 hi-low]

カテゴリー

カレンダー

最新記事

(04/22)

(04/01)

(03/25)

(03/17)

(03/11)

最古記事

プロフィール

HN:

imagerマニア

性別:

非公開