Imager マニア

デジカメ / デジタルビデオカメラ / スマホ用の撮像素子(イメージセンサ/imager/CMOSセンサ)について、マニアな情報や私見を徒然なるままに述べるBlogです(^^;)

[PR]

×

[PR]上記の広告は3ヶ月以上新規記事投稿のないブログに表示されています。新しい記事を書く事で広告が消えます。

オリンパス グローバルシャッター搭載の積層型CMOS開発 ~このセンサのFabもソニー??

ISSCCというのをご存知でしょうか?

毎年2月に米国はサンフランシスコで開催される”半導体回路のオリンピック”と呼ばれる国際会議です。

正式名称は”International Solid-State Circuits Conference”(国際固体素子回路会議)で、採択率は3割前後という超難関。

加えてもう一つ、”動作する実物を作っていないと発表する権利がない”という大きな特徴があります。

つまり、理論上可能かどうか怪しいタイムマシンについては勿論のこと、理屈上は可能なことが十分立証されている短期的未来に作製可能なものであったとしても”モノ”が無いと採択されることはありません。

過去にはこんなソニーの超高速読み出しのデジタル出力センサが発表されましたし、今年もソニーやパナソニックからも報告があり、センサ分野で全9件の発表中、日本勢が半数以上の5件を占めるという”日本電機業界最後の砦”を地で行く強さです(^^)。

さて、前置きが長くなりました。

今回は、そんなISSCCから、オリンパスが報告したセンサ(撮像素子/CMOSイメージセンサ/imager)を採り挙げてみたいと思います。

オリンパスは今回、”グローバルシャッター搭載の積層型CMOSセンサ” を報告しました。

しかしながら、結論を先に書きますと、私の誤解が無ければ、完全なグローバルシャッターではないようです。

それでも十分凄い技術ではありますが・・・。

では以下より具体的に。写真は基本上記サイトからの転載となります。

尚、「」内は、私が勝手に資料内容から”こんな説明内容だったんだろうな”という完全な憶測で付記しています(^^;)

ご了承を。

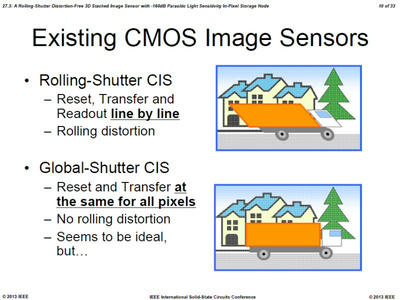

↑ 発表資料をそのまま写真に収めたものと思われます。

恐らく導入部分。「CMOSセンサには元来動体撮影するとローリングシャッター歪みが出ます。グローバルシャッターなら歪みは出ません。何故ならフォトダイオードを全画素同時にリセットして読み出すからです。しかし弱点があります・・・」

う~ん、ISSCCを聴講しにくる様な人にこの説明必要なのか?(^^;)

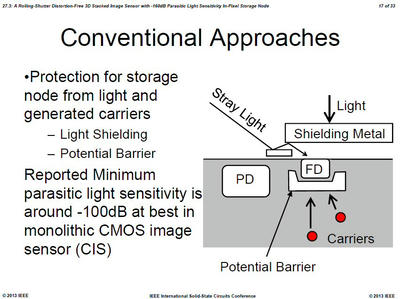

↑ 「従来のグローバルシャッターセンサーは、一時電荷保持容量であるFDを、入射光から守るために遮光したり、またシリコン中からの発生電荷を拾ってしまわないように、ポテンシャルバリアを設けたりしていました。しかし、この様な方式では、過去最小でも-100dB(←入射光に対して10万分の1程度の感度を保持部であるFDが持ってしまっていて、それが次フレームの残像になっていた)程度でした。」

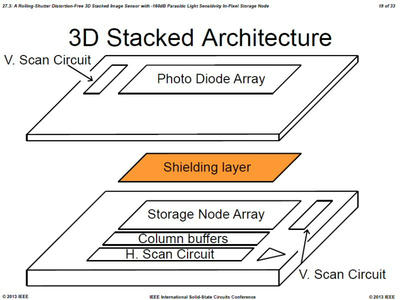

↑ 「そこで今回当社では、フォトダイオードへの入射光から一時電荷保持容量への漏れ光を完全に無くすために、3次元積層構造を採用し、電荷保持容量部をフォトダイオードとは異なる積層レイヤに配置させ、更に積層間に遮光層を設けることにしました」

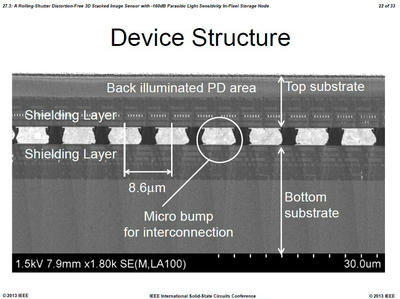

↑「積層構造にするために、上下層を電気的に導通させる必要があり、この写真の様なマイクロバンプを用いて接続しています。バンプ間のピッチは8.6um。直径5um。高さ4umとなっています。」

※5umと4umという数字は元記事より。

また、今回のセンサの画素ピッチは4.3umとなっているようです。

つまり、8.6umというバンプのピッチでは4画素に一つしか、独立した導通を上下レイヤで持つことが出来ません。

そのため、次の等価回路図に出てきますが、4画素でFD部を共有する回路構成となっているようです。

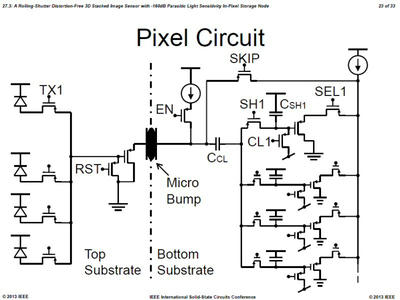

↑ 「画素部の等価回路図です。4画素でFDやSF、リセットトランジスタを共有しています。top基板側にフォトダイオードと転送、リセット、SFトランジスタ、及びFD部を配置。bottom基板側にグローバルシャッタ動作に必要な一時電荷保持容量部を作りこみました。上下の基板のつなぎ目は画素ソースフォロワの出力ノードをマイクロバンプでつないでいます。」

※後で、この等価回路図で予想されるグローバルシャッタ読み時の駆動タイミングを示しますが、上記等価回路を一瞥してすぐに、残念ながら”4画素同時に読むには加算以外に方法がない=上記セットの4画素に関しては、完全にグローバルシャッターを実現出来ていない”ということがわかります。

何故なら、FD及び画素ソースフォロワが4画素に一つしかないため、グローバルシャッタの”全画素同時リセット及び読み出し”の読み出し側が、同時に行うとどうしても加算になってしまうからです。

恐らく、現状の技術では、まだ4.3umピッチでマイクロバンプで上下レイヤをつなぐことが歩留まり良く出来ないのではないでしょうか。

そのための画素ピッチの丁度倍の8.6umピッチでつなぐことにして、回路は仕方なく4画素共有としたと。

※オリジナル記事の方には、「マイクロバンプの接続の歩留まりは99.9%以上」という信じられないくらいの高い数字が載っています。

この数字を信じるならば、もう少し技術革新すれば、4.3umピッチのバンプ作製も99.9%とは言わないまでも量産可能なレベルにまで引き上げられる可能性は十分ありそうですね。

ちなみに、本回路の駆動を考えるに、等価回路図の”SKIP”は、グローバルシャッタを行わずに従来のローリングシャッタ読みをする際にのみONするスイッチで、ENは逆にグローバルシャッタ読みをする時のみONするスイッチではないかと思います。

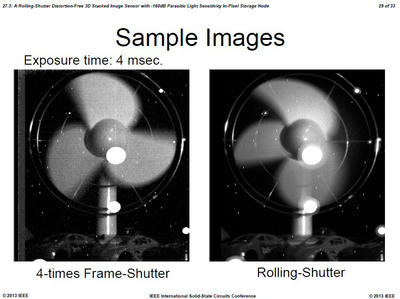

↑ 「実際に本センサで撮影した写真が左になります。右が比較のために従来のローリングシャッタCMOSセンサで撮影したものです。本センサで見事にローリングシャッタ歪みがなくなっているのがお分かりいただけると思います。」

この写真の左側の注釈”4-times Frame-shutter”とはどういう意味でしょうか?

4画素でFD共通のため、4回読み出さないと全画素の絵が取得できないから、4フレーム分読み出したものをエンジンで合成したもの という様な意味でしょうか?

最後のプレゼン資料に出てくる”30fps”は、この4フレーム分を1fpsとカウントした場合のフレームレートなのでしょうか?それとも全画素読み出すには30/4fpsのフレームレートになってしまうのでしょうか?

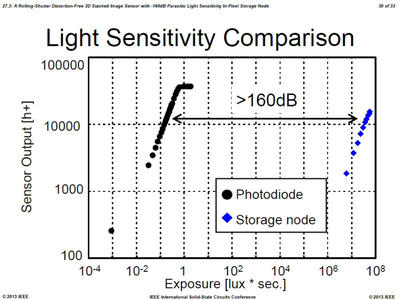

↑ 「本センサのフォトダイオードと電荷保持容量部の感度特性差です。

top基板側にあるフォトダイオードと160dB以上の差が確保されていることがわかります。」

※これは横軸はtop層側から入射させた光量(ルクス×秒)。つまり見方としては、きちんと遮光されたボトム基板側の電荷保持容量部が出す出力は、フォトダイオードと同じ出力を出さそうと思ったら、1億倍の光量を当てなければならず、逆に同じ光量をあてた場合には、フォトダイオードに対して(1/1億)しか出力を出さない≒つまり電荷保持容量部で発生してしまうノイズ(残像)成分は信号に対して(1/1億)しかない良い特性ですよ ということ。

しかし、逆に興味深いのは、ボトム基板側に配置して、かつ間にシールド層を入れたにも関わらず、(1/1億)とはいえ感度を持ってしまうこと(^^;)。いや、「問題となるレベルではない」というご意見には同意します。単に「それでもわずかながら光が届いてしまうんだ」という驚きです。

また、そもそも”従来センサの-100dB”という遮光能力では問題なのでしょうか?

次ページのプレゼン資料で、このセンサの飽和ホール数が30000ホール以上であることが示されます。

仮に飽和の30倍の光量がフォトダイオード面に当たったとして90万ホール。これの10万分の1しか保持容量にホール蓄積されないのだとすると、それでも9ホール程度しか出てこない計算です。

う~ん、断言は出来ませんが、これは太陽か、夜の車のヘッドライトでも撮らない限りは事実上問題ないのでは?

まあ従来センサが本当に-100dBの遮光性能があったかは逆に疑問ですが(^^;)

↑ 書いてからよくよく考えると、前提はメカのシャッターの無いシステムへの組み込みを想定しているセンサの話でしょうから、従来センサの最後に読み出される行は適切な露光量の調節もなく、1フレームの読み出し時間程度光があたりっぱなし。また、そもそもこの課題においてフォトダイオードの飽和がいくらかは本質的には関係ない。

そう考えると、何だかやっぱり-100dB程度では通常使用においても問題が出るような気がしてきました(^^;)

これだとやっぱり

このセンサの電源電圧が何Vなのか不明なため、なんとも言えませんが、3.3Vかもしくは2.8V程度と予想すると、むしろその電源電圧においてグローバルシャッタを実現した上で30000ホールの飽和を確保しているということの方が偉業の様に感じてしまいます。←当然これは積層型にしてフォトダイオードとは別の場所に電荷保持容量を形成できたため、フォトダイオードの面積を圧迫しなくて済んだ恩恵であろうと予想します。

こっちをもっと大々的にアピールした方がいいんじゃないかな?

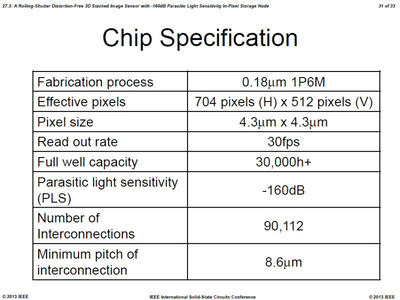

↑ 「最後に本センサのスペックまとめです。」

やっぱり、積層型ともなると6層メタル配線くらい必要になるのですね。この内グローバルシャッターとして増加してしまった分は何メタル分なのでしょうか?

どちらにしても、配線層の増加とそもそも積層型とすることで、かなりなコスト高にはなりそう・・・・・・なのですが、

ソニーは積層型センサを最もコスト競争力が必要そうなスマホ向けに量産しています。

ソニー曰く「top層にはセンサに最適なプロセスを、ボトム側にはロジックに最適なプロセスを それぞれ用いて作製した基板を張り合わせるので、双方を一つの基板に形成するよりも歩留まりが良い」のだとか。

今回のオリンパスのは、この構成だとボトム基板側にもアナログ回路が存在するはずなので、上記と同じ理屈は成り立ちませんが、実際のところは如何なものなのでしょうか?

また、画素数は704×512≒36万画素 程度なので、まだまだ完全に試作レベルですね。←監視カメラ程度なら使える画素数かもしれませんが、監視カメラにわざわざグローバルシャッタセンサを意地で投入する必要はなさそうですし(^^;)。

4.3umピッチでそのままフォーサーズサイズまで引き伸ばせば1200万画素少々ということで、最近のフォーサーズが1600万画素台が主流なので、グローバルシャッター機能を全面に押し出せば、ギリギリ商品性がある画素数のセンサになるように思います。

そこまで考えての開発でしょうか?←期待したいです。

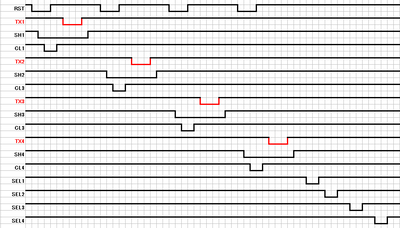

↑ 最後に私が勝手に作成した、このオリンパスセンサのグローバルシャッタ駆動時のタイミングチャートです。

上の等価回路図を合わせてご覧ください。

注!!)このセンサは等価回路図を見ると、どうもホール蓄積型で、画素MOSは全てpMOSで形成されているようです。

そのため、ゲートパルスの極性として、Low=Activeで上記タイミングチャートは記載しています。

細かいところは異なるかもしれませんが、概略動作として合っているのではないかと思っています。

詳細の説明は省きますが、ここで着目したいのは、グローバルシャッタとして重要なフォトダイオードの同時リセットは可能ですが、赤い転送パルス部分が、どうしても4画素同時には出来そうもありません。

注) このチャートの横軸は時間(t)です。

最後になりますが、最大の興味がある疑問を。

”このセンサを作っているFabはどこか?”

ちなみにオリンパスはFabレス会社です。つまり自社で設計はしますが、半導体工場は持っていないため、どこかに依頼しないとセンサ製造自体はムリです。

まともに考えると簡単な消去法でソニーが浮かびそうです。

こんな積層型センサなんて、マニアックな凄いものを、そうそう簡単にいくつものメーカーが作れるようになる気がしませんから・・・・・・

しかし、裏面照射型センサは、あっという間に今や複数の会社が量産していますので、もしかしたらこの積層型センサもソニー製でない可能性も!!??

毎年2月に米国はサンフランシスコで開催される”半導体回路のオリンピック”と呼ばれる国際会議です。

正式名称は”International Solid-State Circuits Conference”(国際固体素子回路会議)で、採択率は3割前後という超難関。

加えてもう一つ、”動作する実物を作っていないと発表する権利がない”という大きな特徴があります。

つまり、理論上可能かどうか怪しいタイムマシンについては勿論のこと、理屈上は可能なことが十分立証されている短期的未来に作製可能なものであったとしても”モノ”が無いと採択されることはありません。

過去にはこんなソニーの超高速読み出しのデジタル出力センサが発表されましたし、今年もソニーやパナソニックからも報告があり、センサ分野で全9件の発表中、日本勢が半数以上の5件を占めるという”日本電機業界最後の砦”を地で行く強さです(^^)。

さて、前置きが長くなりました。

今回は、そんなISSCCから、オリンパスが報告したセンサ(撮像素子/CMOSイメージセンサ/imager)を採り挙げてみたいと思います。

オリンパスは今回、”グローバルシャッター搭載の積層型CMOSセンサ” を報告しました。

しかしながら、結論を先に書きますと、私の誤解が無ければ、完全なグローバルシャッターではないようです。

それでも十分凄い技術ではありますが・・・。

では以下より具体的に。写真は基本上記サイトからの転載となります。

尚、「」内は、私が勝手に資料内容から”こんな説明内容だったんだろうな”という完全な憶測で付記しています(^^;)

ご了承を。

↑ 発表資料をそのまま写真に収めたものと思われます。

恐らく導入部分。「CMOSセンサには元来動体撮影するとローリングシャッター歪みが出ます。グローバルシャッターなら歪みは出ません。何故ならフォトダイオードを全画素同時にリセットして読み出すからです。しかし弱点があります・・・」

う~ん、ISSCCを聴講しにくる様な人にこの説明必要なのか?(^^;)

↑ 「従来のグローバルシャッターセンサーは、一時電荷保持容量であるFDを、入射光から守るために遮光したり、またシリコン中からの発生電荷を拾ってしまわないように、ポテンシャルバリアを設けたりしていました。しかし、この様な方式では、過去最小でも-100dB(←入射光に対して10万分の1程度の感度を保持部であるFDが持ってしまっていて、それが次フレームの残像になっていた)程度でした。」

↑ 「そこで今回当社では、フォトダイオードへの入射光から一時電荷保持容量への漏れ光を完全に無くすために、3次元積層構造を採用し、電荷保持容量部をフォトダイオードとは異なる積層レイヤに配置させ、更に積層間に遮光層を設けることにしました」

↑「積層構造にするために、上下層を電気的に導通させる必要があり、この写真の様なマイクロバンプを用いて接続しています。バンプ間のピッチは8.6um。直径5um。高さ4umとなっています。」

※5umと4umという数字は元記事より。

また、今回のセンサの画素ピッチは4.3umとなっているようです。

つまり、8.6umというバンプのピッチでは4画素に一つしか、独立した導通を上下レイヤで持つことが出来ません。

そのため、次の等価回路図に出てきますが、4画素でFD部を共有する回路構成となっているようです。

↑ 「画素部の等価回路図です。4画素でFDやSF、リセットトランジスタを共有しています。top基板側にフォトダイオードと転送、リセット、SFトランジスタ、及びFD部を配置。bottom基板側にグローバルシャッタ動作に必要な一時電荷保持容量部を作りこみました。上下の基板のつなぎ目は画素ソースフォロワの出力ノードをマイクロバンプでつないでいます。」

※後で、この等価回路図で予想されるグローバルシャッタ読み時の駆動タイミングを示しますが、上記等価回路を一瞥してすぐに、残念ながら”4画素同時に読むには加算以外に方法がない=上記セットの4画素に関しては、完全にグローバルシャッターを実現出来ていない”ということがわかります。

何故なら、FD及び画素ソースフォロワが4画素に一つしかないため、グローバルシャッタの”全画素同時リセット及び読み出し”の読み出し側が、同時に行うとどうしても加算になってしまうからです。

恐らく、現状の技術では、まだ4.3umピッチでマイクロバンプで上下レイヤをつなぐことが歩留まり良く出来ないのではないでしょうか。

そのための画素ピッチの丁度倍の8.6umピッチでつなぐことにして、回路は仕方なく4画素共有としたと。

※オリジナル記事の方には、「マイクロバンプの接続の歩留まりは99.9%以上」という信じられないくらいの高い数字が載っています。

この数字を信じるならば、もう少し技術革新すれば、4.3umピッチのバンプ作製も99.9%とは言わないまでも量産可能なレベルにまで引き上げられる可能性は十分ありそうですね。

ちなみに、本回路の駆動を考えるに、等価回路図の”SKIP”は、グローバルシャッタを行わずに従来のローリングシャッタ読みをする際にのみONするスイッチで、ENは逆にグローバルシャッタ読みをする時のみONするスイッチではないかと思います。

↑ 「実際に本センサで撮影した写真が左になります。右が比較のために従来のローリングシャッタCMOSセンサで撮影したものです。本センサで見事にローリングシャッタ歪みがなくなっているのがお分かりいただけると思います。」

この写真の左側の注釈”4-times Frame-shutter”とはどういう意味でしょうか?

4画素でFD共通のため、4回読み出さないと全画素の絵が取得できないから、4フレーム分読み出したものをエンジンで合成したもの という様な意味でしょうか?

最後のプレゼン資料に出てくる”30fps”は、この4フレーム分を1fpsとカウントした場合のフレームレートなのでしょうか?それとも全画素読み出すには30/4fpsのフレームレートになってしまうのでしょうか?

↑ 「本センサのフォトダイオードと電荷保持容量部の感度特性差です。

top基板側にあるフォトダイオードと160dB以上の差が確保されていることがわかります。」

※これは横軸はtop層側から入射させた光量(ルクス×秒)。つまり見方としては、きちんと遮光されたボトム基板側の電荷保持容量部が出す出力は、フォトダイオードと同じ出力を出さそうと思ったら、1億倍の光量を当てなければならず、逆に同じ光量をあてた場合には、フォトダイオードに対して(1/1億)しか出力を出さない≒つまり電荷保持容量部で発生してしまうノイズ(残像)成分は信号に対して(1/1億)しかない良い特性ですよ ということ。

しかし、逆に興味深いのは、ボトム基板側に配置して、かつ間にシールド層を入れたにも関わらず、(1/1億)とはいえ感度を持ってしまうこと(^^;)。いや、「問題となるレベルではない」というご意見には同意します。単に「それでもわずかながら光が届いてしまうんだ」という驚きです。

次ページのプレゼン資料で、このセンサの飽和ホール数が30000ホール以上であることが示されます。

仮に飽和の30倍の光量がフォトダイオード面に当たったとして90万ホール。これの10万分の1しか保持容量にホール蓄積されないのだとすると、それでも9ホール程度しか出てこない計算です。

う~ん、断言は出来ませんが、これは太陽か、夜の車のヘッドライトでも撮らない限りは事実上問題ないのでは?

まあ従来センサが本当に-100dBの遮光性能があったかは逆に疑問ですが(^^;)

↑ 書いてからよくよく考えると、前提はメカのシャッターの無いシステムへの組み込みを想定しているセンサの話でしょうから、従来センサの最後に読み出される行は適切な露光量の調節もなく、1フレームの読み出し時間程度光があたりっぱなし。また、そもそもこの課題においてフォトダイオードの飽和がいくらかは本質的には関係ない。

そう考えると、何だかやっぱり-100dB程度では通常使用においても問題が出るような気がしてきました(^^;)

これだとやっぱり

このセンサの電源電圧が何Vなのか不明なため、なんとも言えませんが、3.3Vかもしくは2.8V程度と予想すると、むしろその電源電圧においてグローバルシャッタを実現した上で30000ホールの飽和を確保しているということの方が偉業の様に感じてしまいます。←当然これは積層型にしてフォトダイオードとは別の場所に電荷保持容量を形成できたため、フォトダイオードの面積を圧迫しなくて済んだ恩恵であろうと予想します。

こっちをもっと大々的にアピールした方がいいんじゃないかな?

↑ 「最後に本センサのスペックまとめです。」

やっぱり、積層型ともなると6層メタル配線くらい必要になるのですね。この内グローバルシャッターとして増加してしまった分は何メタル分なのでしょうか?

どちらにしても、配線層の増加とそもそも積層型とすることで、かなりなコスト高にはなりそう・・・・・・なのですが、

ソニーは積層型センサを最もコスト競争力が必要そうなスマホ向けに量産しています。

ソニー曰く「top層にはセンサに最適なプロセスを、ボトム側にはロジックに最適なプロセスを それぞれ用いて作製した基板を張り合わせるので、双方を一つの基板に形成するよりも歩留まりが良い」のだとか。

今回のオリンパスのは、この構成だとボトム基板側にもアナログ回路が存在するはずなので、上記と同じ理屈は成り立ちませんが、実際のところは如何なものなのでしょうか?

また、画素数は704×512≒36万画素 程度なので、まだまだ完全に試作レベルですね。←監視カメラ程度なら使える画素数かもしれませんが、監視カメラにわざわざグローバルシャッタセンサを意地で投入する必要はなさそうですし(^^;)。

4.3umピッチでそのままフォーサーズサイズまで引き伸ばせば1200万画素少々ということで、最近のフォーサーズが1600万画素台が主流なので、グローバルシャッター機能を全面に押し出せば、ギリギリ商品性がある画素数のセンサになるように思います。

そこまで考えての開発でしょうか?←期待したいです。

↑ 最後に私が勝手に作成した、このオリンパスセンサのグローバルシャッタ駆動時のタイミングチャートです。

上の等価回路図を合わせてご覧ください。

注!!)このセンサは等価回路図を見ると、どうもホール蓄積型で、画素MOSは全てpMOSで形成されているようです。

そのため、ゲートパルスの極性として、Low=Activeで上記タイミングチャートは記載しています。

細かいところは異なるかもしれませんが、概略動作として合っているのではないかと思っています。

詳細の説明は省きますが、ここで着目したいのは、グローバルシャッタとして重要なフォトダイオードの同時リセットは可能ですが、赤い転送パルス部分が、どうしても4画素同時には出来そうもありません。

注) このチャートの横軸は時間(t)です。

最後になりますが、最大の興味がある疑問を。

”このセンサを作っているFabはどこか?”

ちなみにオリンパスはFabレス会社です。つまり自社で設計はしますが、半導体工場は持っていないため、どこかに依頼しないとセンサ製造自体はムリです。

まともに考えると簡単な消去法でソニーが浮かびそうです。

こんな積層型センサなんて、マニアックな凄いものを、そうそう簡単にいくつものメーカーが作れるようになる気がしませんから・・・・・・

しかし、裏面照射型センサは、あっという間に今や複数の会社が量産していますので、もしかしたらこの積層型センサもソニー製でない可能性も!!??

PR

コメント

ブログ内検索

カウンター

最新コメント

[03/28 hoge]

[03/26 hi-low]

[03/22 山川]

[03/18 hoge]

[03/08 hi-low]

[03/04 hoge]

[02/26 山川]

[02/26 山川]

[02/19 hoge]

[02/18 山川]

[02/05 hoge]

[02/05 hi-low]

[01/29 通りすがりです]

[01/28 FT]

[01/23 hi-low]

カテゴリー

カレンダー

最新記事

(04/22)

(04/01)

(03/25)

(03/17)

(03/11)

最古記事

プロフィール

HN:

imagerマニア

性別:

非公開