Imager マニア

デジカメ / デジタルビデオカメラ / スマホ用の撮像素子(イメージセンサ/imager/CMOSセンサ)について、マニアな情報や私見を徒然なるままに述べるBlogです(^^;)

[PR]

×

[PR]上記の広告は3ヶ月以上新規記事投稿のないブログに表示されています。新しい記事を書く事で広告が消えます。

SamsungとOmniVisionのStacked CIS ~特にオムニビジョンとTSMCの連携と構想

今回は、前回エントリ(ソニーのStacked CIS)に続き、Samsung(サムスン)とOmniVision(オムニビジョン)の積層型センサのお話です。

ただし、上記2社に関しては具体的な構造等の情報を私は持ち合わせていない点ご了承ください。

まず、発表ページを見ると、ソニーに次いで既にStacked センサ(積層型センサ)の製造・販売実績があるSamsung。

↑ Samsungの13Mpixelセンサ写真

(↑スマホ用途なはずで、この写真のパッケージングは明らかに試作か、顧客が性能評価を試す用のテストサンプル用途ですね)

上記写真下の一文

”This Smart WDR feature is based on Samsung’s advanced 65nm stacked process, where the pixel array is attached right on top of the logic circuit”

ただし、上記2社に関しては具体的な構造等の情報を私は持ち合わせていない点ご了承ください。

まず、発表ページを見ると、ソニーに次いで既にStacked センサ(積層型センサ)の製造・販売実績があるSamsung。

↑ Samsungの13Mpixelセンサ写真

(↑スマホ用途なはずで、この写真のパッケージングは明らかに試作か、顧客が性能評価を試す用のテストサンプル用途ですね)

上記写真下の一文

”This Smart WDR feature is based on Samsung’s advanced 65nm stacked process, where the pixel array is attached right on top of the logic circuit”

このSmart ワイドダイナミックレンジの特長は、サムスンの先進的な65nm積層型プロセスがベースになっている。その積層型プロセスとは、画素アレイがロジック回路の上に取り付けられている

文字だけしか情報が無いので本当かどうか確認しようが無いのですが、上の英文はどう解釈しても私にはソニーの積層型CISと同じことを行っているようにしか読めませんでした。

(つまり、イメージセンサに一緒に積層されたロジック回路によって、WDR処理を施していると)

以前エントリのサムスンGalaxyS5搭載撮像素子のチップワークス解析断面写真には、上記の様な積層型センサの件は一切触れられていませんでしたが、この写真の上方に別のロジックチップがattachされていたのでしょうか?

それともstacked CIS構造になっているのは、(何等かの理由により)上の写真の13Mpixel版のセンサのみなのでしょうか?

↓ ちなみに、以下写真が、Samsungの16MPixel版の様です。

何で同じセンサの写真を複数個合わせて掲載するのでしょうね?

しかも16M版の方は、1チップだけ向き逆で撮影。

一瞬2種類のセンサがあるのかと思いました(^^;)

ちなみに本話題には全く関係ありませんが、双方の画素数版とも、

センサパッドは3辺にしか存在しないようですね。

(つまり正規のパッケージング後にも、パッケージの3辺にしか入出力ピンが存在しない)

スマホ用途の様な面積が小さいことが求められるだろうセンサにおいては、もしかしたら受け側の実装面積も含めて面積縮小に貢献しているかもしれませんね。

お次はOmniVision。

以下の情報の出元は、前回同様Yole developmentなる会社。

↑上記資料は、OmniVisionのCTOが、2014年、ロンドンで開催されたImage Sensor Conferenceという場において、”The Future of CMOS Imaging”と題したプレゼンテーションで用いたものの様です。

まずは、今までのCMOSイメージセンサの技術的なトレンドと今後という様な表です。

横軸年代。縦軸はセンサ画素数(単位:Mpix)。

※恐らく、これはOmnivision社としての年代表であって、他の会社含めた技術的な遷移では無いと思われます。

↑そうしないと、表の技術と年代が符合しない箇所が出てきてしまいます。

1997年頃:初めてCMOS image sensor の画素数が100万画素に到達

2002年頃:1画素に4つのトランジスタを配し、かつ埋め込みフォトダイオード構造を採用

(※それまでは3T構造かつフォトダイオードが埋め込み構造ではなかった。

一般に、この時の3T構造は転送トランジスタが無く、フォトダイオードからの完全転送が不能。かつ、埋め込みフォトダイオードで無い場合、シリコン表面にフォトダイオードが剥き出しのため、欠陥の多い表面からのノイズをモロに拾ってしまい、画質的に難があった)

2005年頃:Pixel Sharing Archtecture 採用

(※画素内のフォトダイオードの面積を最大限確保するために、画素トランジスタを隣接する複数の画素でshareする方式。具体的には4Tの場合は、行選択トランジスタ、リセットトランジスタ、画素ソースフォロワ(アンプ)の3つを共用する回路及び駆動方式)

2008年頃:BSI構造採用

この表が正しければ、私の感覚では、この辺で業界top水準の技術トレンドにOmniVisionが追いついた感じがします。

2015年頃:Hybrid Stacking 構造採用

↑これが以下資料から出てくるのですが、いわゆるソニーやSamsungが採用するStacked CIS(積層型CMOSイメージセンサ)のことの様です。

ですので、恐らくオムニビジョンは、積層型センサについてはまだ2社に対して遅れていて、量産までは行っていないと思われます。

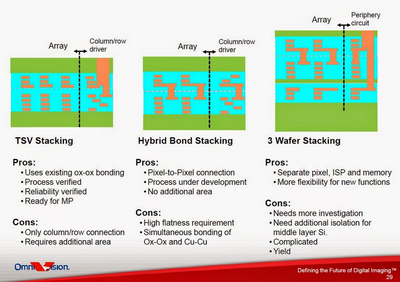

↑ これを見ると、オムニビジョンは主に3種類、もしくは三段階のstacked構造を考えている様です。

まず、一番左の構造は、現在のソニーの積層型センサの構造と同じものだと思われます。

画素単位では積層されたロジック回路用ウェハには導通させず、列回路及び行駆動回路部分でのみ(つまり画素領域外の周辺回路部分でのみ)topウェハとbottomウェハの回路同士を導通させる構造です。

以下OmniVisionの見解です。

Pros / Cons = いわゆる”良い点”、”悪い点”ですが、

Pros:

・既に現存する酸化膜同士の貼り合わせを使える

・プロセス確認済 (≒実証済み。以下同様)

・信頼性確認済み

・MP(Mass Production:量産)準備OK

Cons:

・列と行でしか(topウェハとbottomウェハの回路の)接続不能

・(恐らく他の方式と比較して相対的に、回路などのための)追加の領域が必要

次に中央のタイプ

これは、ソニーが現在量産しているタイプより進んでいて、

周辺回路部分のみでなく、”画素単位でも”topウェハとbottomウェハの電気的導通を確保可能なタイプの様です。

完璧ではありませんでしたが、以前2013年のISSCCにおいてオリンパスが発表したグローバルシャッタセンサが、”4画素に一つの割合で”topウェハとbottomウェハを”Micro bump”と彼らが呼ぶ方式で接続させた積層型センサでした。

↑この時、4画素に一つの割合で”しか”topとbottomウェハを接続しなかったのは、間違い無く”したかったけれど、技術的にそんな微細な接続を出来なかった”ということだと思われます。

オムニビジョンはスマホカメラ用途センサに強いメーカーで、スマホカメラは通常微細画素センサですから、このオムニビジョンが考える中央の積層型センサの画素同士の接続というのは、1um台の画素ピッチにおいても画素単位で接続可能な技術を考えていると予想します。

また、最近見てきたNHK技研公開での画素AD搭載&三次元構造狙いのセンサ。

↑こちらでも、画素単位で、しかも複数ウェハ枚数を接続したいと狙っていました。

このOmniVisionの考える構造が実現すれば、こちらのNHKのセンサも技術ハードルを一つクリア出来ることになります。

Pros:

・画素単位で接続可能

・プロセス開発中

・追加areaの必要無し

Cons:

・かなりな平坦性が要求される

↑※画素単位で微細な孔開けが必要になるため、最低でもチップ面内で(実際にはウェハ面内で)相当均一な膜厚に出来ていないと、

薄いところと厚いところが出来た場合、孔開けの露光時にどちらかにしかフォーカスが合わず、結果合わなかった方が、狙った通りの太さや形状にならなかったり、最悪孔が開かなかったりするためと思われます

・酸化膜同士、及び銅配線同士を同時に接続しなければならない

↑※左の積層型タイプの断面模式図と比較してもらえればわかるのですが、左のタイプは周辺回路でtopとbottomウェハを接続する際に、

まず最初にウェハの酸化膜同士を接続し、その後、表面から二つのウェハの金属配線に対して同じ穴を開け、そこに導電物質を埋めれば電気的導通が確保されます。

(つまり、実質接続するのは酸化膜同士だけですし、もしくはCu配線同士は後から接続で済みます)

対して、中央の積層型の場合には、左のタイプの酸化膜同士の接続に加え、画素内の金属配線同士を同時に接続しなければなりません。

後から画素に穴を開けて導通させることは、技術的には可能かもしれませんが、出来たとしても撮像素子としての体を成さなくなるので本末転倒です(^^;)。

最後に一番右のタイプ。

左と中央のタイプの合わせ技ですね。ウェハとしては、3ウェハの貼り合わせとなります。

画素単位同士で接続し、更に周辺回路部は、topからbottomのロジック回路へ、bottomの駆動回路からtopへの接続も可能となる想定だと思われます。

Pros:

・画素と、ISP(Image Signal Processor)及びメモリとを(top基板とbottom基板に)分離可能

・新しい機能投入に対してよりフレキシビリティが高い

Cons:

・ニーズがあるかもっと調査が必要

・Middle layer Siのより(強力な?)分離の必要性

・複雑

・歩留まり

悪い点(Cons)の、一つ目と三つ目は「それを言っちゃぁ身も蓋も無い」と突っ込みたくなります(笑)。何か素直というか。

一つ目は、これをこの場で言うことにより、逆に「こういうのを仕込んでくれれば助かる」という機器メーカーからの声を逆にもらおうという狙いなのでしょうか。

そして二つ目の分離の必要性が私にはいまひとつピンときません。

左の二つと何が異なるのでしょうか。

(前提として、一番右のタイプにのみ、ISPなどの熱源となりそうな回路をbottom側に載せるという前提?)

結局、今のところ一番左のタイプは、ソニーで量産実績もあり、この資料でも量産準備OKということなので、OmniVisionでもそれなりに実現可能性が高いのでしょうが、中央は”プロセス開発中”、右のに至っては”ニーズがあるか調査中”(^^;)とのことで、どの程度の次期に実現されるのか(はたまた実現されないのか)微妙な感じですね。

また、ここまで”OmniVisionの”という風に表現してきましたが、積層型センサというのは実はほとんどプロセス技術に拠る開発であり、

オムニビジョンはFabレスメーカーなため、実はオムニビジョンが何か具体的に開発を行う訳では恐らくなくて、

実際には、TSMC(台湾 Semiconductor Manufacturing Co., Ltd)がこれら開発を担っているはずです。

というのは、以前hmbさんに「オムニビジョンはTSMCがFabです」という風に教わったからです。

上記資料を見ると、「「OmniVision と TSMC は CMOS イメージセンサー開発において、長期にわたりパートナー関係を維持しています。」

となっていますので、今現在においても、OmniVisionのセンサ製造FabはTSMCと考えるのが妥当だと思います。

こうやって見てみると、ソニーが積層型センサを先駆けて開発し、それに対して遅れはしたもののSamsungとOmniVisionは追随して積層型センサを実現、もしくは実現させられそうなところまできています。

対して上記会社に次ぐポジションにいたと思われるAptinaからはその様(Stacked CIS)な話を聞いたことがありませんでした。

最近、AptinaはONSemiconductorに買われましたが、もしかしたら、積層型CMOSイメージセンサ技術の技術開発もしくは設備投資についていけない(そのせいで今後のイメージセンサのコスト競争についていけない)との判断も、買われることを決断した理由の一つにあるのかもしれませんね。

最後に、上記資料写真が載っていたサイトの(積層型センサと関係ありませんが)他の写真図面もせっかくなので備忘録的に載せておきます。

↑ オムニビジョンのFSI(左)からOmniBSIと名前をつけている裏面照射型センサ(中)から、OmniBSI-2と進化する右の画素断面図と思われるもの。

図面だけ見ると、OmniBSIとOmniBSI-2の違いって何?(笑)

配線の色が赤から黄土色に変わって、かつ受光部下の配線に穴が開いている!?

文面を合わせて読むと、辛うじて配線の色が変わっているのは、恐らく

赤:Al (アルミ)

黄土色:Cu (銅)

の違いを表しているのだろうとわかるのですが、OmniBSI-2の受光部下の配線に穴が開いている図が言いたいことが本当にわかりません(^^;)

また、(元の文章と合わせて読んで)1.1um画素ピッチ、65nmプロセスにおいて初めて300mmウェハとCu配線に移行したというのも少々意外でした。

確かCPU等のICは、もっと以前のプロセス世代からカッパー配線でかつ300mmウェハを使用していたと記憶しているので、何となく撮像素子も同じ道をたどっているものだと漠然と考えていました。

↑ オムニビジョンの画素ピッチと画素数のトレンドライン

少し前のエントリのコメント欄において画素ピッチはどこまで小さくなるのだ?もしくはどこまで小さくすることに意味があるのだ?的な話になりましたが、

少なくとも、今のところOmniVisionは、2015年に0.9um□画素ピッチの30Mpix超えを考えているようです。

文字だけしか情報が無いので本当かどうか確認しようが無いのですが、上の英文はどう解釈しても私にはソニーの積層型CISと同じことを行っているようにしか読めませんでした。

(つまり、イメージセンサに一緒に積層されたロジック回路によって、WDR処理を施していると)

以前エントリのサムスンGalaxyS5搭載撮像素子のチップワークス解析断面写真には、上記の様な積層型センサの件は一切触れられていませんでしたが、この写真の上方に別のロジックチップがattachされていたのでしょうか?

それともstacked CIS構造になっているのは、(何等かの理由により)上の写真の13Mpixel版のセンサのみなのでしょうか?

↓ ちなみに、以下写真が、Samsungの16MPixel版の様です。

何で同じセンサの写真を複数個合わせて掲載するのでしょうね?

しかも16M版の方は、1チップだけ向き逆で撮影。

一瞬2種類のセンサがあるのかと思いました(^^;)

ちなみに本話題には全く関係ありませんが、双方の画素数版とも、

センサパッドは3辺にしか存在しないようですね。

(つまり正規のパッケージング後にも、パッケージの3辺にしか入出力ピンが存在しない)

スマホ用途の様な面積が小さいことが求められるだろうセンサにおいては、もしかしたら受け側の実装面積も含めて面積縮小に貢献しているかもしれませんね。

お次はOmniVision。

以下の情報の出元は、前回同様Yole developmentなる会社。

↑上記資料は、OmniVisionのCTOが、2014年、ロンドンで開催されたImage Sensor Conferenceという場において、”The Future of CMOS Imaging”と題したプレゼンテーションで用いたものの様です。

まずは、今までのCMOSイメージセンサの技術的なトレンドと今後という様な表です。

横軸年代。縦軸はセンサ画素数(単位:Mpix)。

※恐らく、これはOmnivision社としての年代表であって、他の会社含めた技術的な遷移では無いと思われます。

↑そうしないと、表の技術と年代が符合しない箇所が出てきてしまいます。

1997年頃:初めてCMOS image sensor の画素数が100万画素に到達

2002年頃:1画素に4つのトランジスタを配し、かつ埋め込みフォトダイオード構造を採用

(※それまでは3T構造かつフォトダイオードが埋め込み構造ではなかった。

一般に、この時の3T構造は転送トランジスタが無く、フォトダイオードからの完全転送が不能。かつ、埋め込みフォトダイオードで無い場合、シリコン表面にフォトダイオードが剥き出しのため、欠陥の多い表面からのノイズをモロに拾ってしまい、画質的に難があった)

2005年頃:Pixel Sharing Archtecture 採用

(※画素内のフォトダイオードの面積を最大限確保するために、画素トランジスタを隣接する複数の画素でshareする方式。具体的には4Tの場合は、行選択トランジスタ、リセットトランジスタ、画素ソースフォロワ(アンプ)の3つを共用する回路及び駆動方式)

2008年頃:BSI構造採用

この表が正しければ、私の感覚では、この辺で業界top水準の技術トレンドにOmniVisionが追いついた感じがします。

2015年頃:Hybrid Stacking 構造採用

↑これが以下資料から出てくるのですが、いわゆるソニーやSamsungが採用するStacked CIS(積層型CMOSイメージセンサ)のことの様です。

ですので、恐らくオムニビジョンは、積層型センサについてはまだ2社に対して遅れていて、量産までは行っていないと思われます。

↑ これを見ると、オムニビジョンは主に3種類、もしくは三段階のstacked構造を考えている様です。

まず、一番左の構造は、現在のソニーの積層型センサの構造と同じものだと思われます。

画素単位では積層されたロジック回路用ウェハには導通させず、列回路及び行駆動回路部分でのみ(つまり画素領域外の周辺回路部分でのみ)topウェハとbottomウェハの回路同士を導通させる構造です。

以下OmniVisionの見解です。

Pros / Cons = いわゆる”良い点”、”悪い点”ですが、

Pros:

・既に現存する酸化膜同士の貼り合わせを使える

・プロセス確認済 (≒実証済み。以下同様)

・信頼性確認済み

・MP(Mass Production:量産)準備OK

Cons:

・列と行でしか(topウェハとbottomウェハの回路の)接続不能

・(恐らく他の方式と比較して相対的に、回路などのための)追加の領域が必要

次に中央のタイプ

これは、ソニーが現在量産しているタイプより進んでいて、

周辺回路部分のみでなく、”画素単位でも”topウェハとbottomウェハの電気的導通を確保可能なタイプの様です。

完璧ではありませんでしたが、以前2013年のISSCCにおいてオリンパスが発表したグローバルシャッタセンサが、”4画素に一つの割合で”topウェハとbottomウェハを”Micro bump”と彼らが呼ぶ方式で接続させた積層型センサでした。

↑この時、4画素に一つの割合で”しか”topとbottomウェハを接続しなかったのは、間違い無く”したかったけれど、技術的にそんな微細な接続を出来なかった”ということだと思われます。

オムニビジョンはスマホカメラ用途センサに強いメーカーで、スマホカメラは通常微細画素センサですから、このオムニビジョンが考える中央の積層型センサの画素同士の接続というのは、1um台の画素ピッチにおいても画素単位で接続可能な技術を考えていると予想します。

また、最近見てきたNHK技研公開での画素AD搭載&三次元構造狙いのセンサ。

↑こちらでも、画素単位で、しかも複数ウェハ枚数を接続したいと狙っていました。

このOmniVisionの考える構造が実現すれば、こちらのNHKのセンサも技術ハードルを一つクリア出来ることになります。

Pros:

・画素単位で接続可能

・プロセス開発中

・追加areaの必要無し

Cons:

・かなりな平坦性が要求される

↑※画素単位で微細な孔開けが必要になるため、最低でもチップ面内で(実際にはウェハ面内で)相当均一な膜厚に出来ていないと、

薄いところと厚いところが出来た場合、孔開けの露光時にどちらかにしかフォーカスが合わず、結果合わなかった方が、狙った通りの太さや形状にならなかったり、最悪孔が開かなかったりするためと思われます

・酸化膜同士、及び銅配線同士を同時に接続しなければならない

↑※左の積層型タイプの断面模式図と比較してもらえればわかるのですが、左のタイプは周辺回路でtopとbottomウェハを接続する際に、

まず最初にウェハの酸化膜同士を接続し、その後、表面から二つのウェハの金属配線に対して同じ穴を開け、そこに導電物質を埋めれば電気的導通が確保されます。

(つまり、実質接続するのは酸化膜同士だけですし、もしくはCu配線同士は後から接続で済みます)

対して、中央の積層型の場合には、左のタイプの酸化膜同士の接続に加え、画素内の金属配線同士を同時に接続しなければなりません。

後から画素に穴を開けて導通させることは、技術的には可能かもしれませんが、出来たとしても撮像素子としての体を成さなくなるので本末転倒です(^^;)。

最後に一番右のタイプ。

左と中央のタイプの合わせ技ですね。ウェハとしては、3ウェハの貼り合わせとなります。

画素単位同士で接続し、更に周辺回路部は、topからbottomのロジック回路へ、bottomの駆動回路からtopへの接続も可能となる想定だと思われます。

Pros:

・画素と、ISP(Image Signal Processor)及びメモリとを(top基板とbottom基板に)分離可能

・新しい機能投入に対してよりフレキシビリティが高い

Cons:

・ニーズがあるかもっと調査が必要

・Middle layer Siのより(強力な?)分離の必要性

・複雑

・歩留まり

悪い点(Cons)の、一つ目と三つ目は「それを言っちゃぁ身も蓋も無い」と突っ込みたくなります(笑)。何か素直というか。

一つ目は、これをこの場で言うことにより、逆に「こういうのを仕込んでくれれば助かる」という機器メーカーからの声を逆にもらおうという狙いなのでしょうか。

そして二つ目の分離の必要性が私にはいまひとつピンときません。

左の二つと何が異なるのでしょうか。

(前提として、一番右のタイプにのみ、ISPなどの熱源となりそうな回路をbottom側に載せるという前提?)

結局、今のところ一番左のタイプは、ソニーで量産実績もあり、この資料でも量産準備OKということなので、OmniVisionでもそれなりに実現可能性が高いのでしょうが、中央は”プロセス開発中”、右のに至っては”ニーズがあるか調査中”(^^;)とのことで、どの程度の次期に実現されるのか(はたまた実現されないのか)微妙な感じですね。

また、ここまで”OmniVisionの”という風に表現してきましたが、積層型センサというのは実はほとんどプロセス技術に拠る開発であり、

オムニビジョンはFabレスメーカーなため、実はオムニビジョンが何か具体的に開発を行う訳では恐らくなくて、

実際には、TSMC(台湾 Semiconductor Manufacturing Co., Ltd)がこれら開発を担っているはずです。

というのは、以前hmbさんに「オムニビジョンはTSMCがFabです」という風に教わったからです。

上記資料を見ると、「「OmniVision と TSMC は CMOS イメージセンサー開発において、長期にわたりパートナー関係を維持しています。」

となっていますので、今現在においても、OmniVisionのセンサ製造FabはTSMCと考えるのが妥当だと思います。

こうやって見てみると、ソニーが積層型センサを先駆けて開発し、それに対して遅れはしたもののSamsungとOmniVisionは追随して積層型センサを実現、もしくは実現させられそうなところまできています。

対して上記会社に次ぐポジションにいたと思われるAptinaからはその様(Stacked CIS)な話を聞いたことがありませんでした。

最近、AptinaはONSemiconductorに買われましたが、もしかしたら、積層型CMOSイメージセンサ技術の技術開発もしくは設備投資についていけない(そのせいで今後のイメージセンサのコスト競争についていけない)との判断も、買われることを決断した理由の一つにあるのかもしれませんね。

最後に、上記資料写真が載っていたサイトの(積層型センサと関係ありませんが)他の写真図面もせっかくなので備忘録的に載せておきます。

↑ オムニビジョンのFSI(左)からOmniBSIと名前をつけている裏面照射型センサ(中)から、OmniBSI-2と進化する右の画素断面図と思われるもの。

図面だけ見ると、OmniBSIとOmniBSI-2の違いって何?(笑)

配線の色が赤から黄土色に変わって、かつ受光部下の配線に穴が開いている!?

文面を合わせて読むと、辛うじて配線の色が変わっているのは、恐らく

赤:Al (アルミ)

黄土色:Cu (銅)

の違いを表しているのだろうとわかるのですが、OmniBSI-2の受光部下の配線に穴が開いている図が言いたいことが本当にわかりません(^^;)

また、(元の文章と合わせて読んで)1.1um画素ピッチ、65nmプロセスにおいて初めて300mmウェハとCu配線に移行したというのも少々意外でした。

確かCPU等のICは、もっと以前のプロセス世代からカッパー配線でかつ300mmウェハを使用していたと記憶しているので、何となく撮像素子も同じ道をたどっているものだと漠然と考えていました。

↑ オムニビジョンの画素ピッチと画素数のトレンドライン

少し前のエントリのコメント欄において画素ピッチはどこまで小さくなるのだ?もしくはどこまで小さくすることに意味があるのだ?的な話になりましたが、

少なくとも、今のところOmniVisionは、2015年に0.9um□画素ピッチの30Mpix超えを考えているようです。

PR

ブログ内検索

カウンター

最新コメント

[03/28 hoge]

[03/26 hi-low]

[03/22 山川]

[03/18 hoge]

[03/08 hi-low]

[03/04 hoge]

[02/26 山川]

[02/26 山川]

[02/19 hoge]

[02/18 山川]

[02/05 hoge]

[02/05 hi-low]

[01/29 通りすがりです]

[01/28 FT]

[01/23 hi-low]

カテゴリー

カレンダー

最新記事

(04/22)

(04/01)

(03/25)

(03/17)

(03/11)

最古記事

プロフィール

HN:

imagerマニア

性別:

非公開