Imager マニア

デジカメ / デジタルビデオカメラ / スマホ用の撮像素子(イメージセンサ/imager/CMOSセンサ)について、マニアな情報や私見を徒然なるままに述べるBlogです(^^;)

[PR]

×

[PR]上記の広告は3ヶ月以上新規記事投稿のないブログに表示されています。新しい記事を書く事で広告が消えます。

スマホ&タブレット搭載カメラメーカーの勝者は? ~2012 chipworks技術blogより

カナダのチップ解析会社chipworksからしばらく前にタイトルの様な技術blogがupされています。

スマホやタブレットに搭載されているものですので、ここで言う”カメラ”というのは、ほとんどレンズを除けばセンサ(撮像素子/イメージセンサ/imager)と同値だと思います。

ので、imagerマニアとしては大変興味ある対象です。

ですので、例によって以下意訳したいと思います。

(↑と言っても、今回は技術的な分析内容はなく、ほぼ図でこと足りますので、意訳もかなりざっくり適当です。ご容赦を(^^;))

↑ chipworksが2012年の一年間で、解析(分解)した”スマホ及びタブレット端末自体の”の製造会社比率

スマホやタブレットに搭載されているものですので、ここで言う”カメラ”というのは、ほとんどレンズを除けばセンサ(撮像素子/イメージセンサ/imager)と同値だと思います。

ので、imagerマニアとしては大変興味ある対象です。

ですので、例によって以下意訳したいと思います。

(↑と言っても、今回は技術的な分析内容はなく、ほぼ図でこと足りますので、意訳もかなりざっくり適当です。ご容赦を(^^;))

↑ chipworksが2012年の一年間で、解析(分解)した”スマホ及びタブレット端末自体の”の製造会社比率

PR

ソニー 積層型裏面照射センサ(ExmorRS) ~ISSCC2013 & chipworks

ISSCC2013の第二弾。

ソニーの積層型裏面照射センサ(ExmorRS)ネタです。

(ISSCCについてはこちらのエントリの冒頭を参照ください)

以前、ソニーのスマホ搭載の積層型裏面センサの動画HDR(ハイダイナミックレンジ)機能については採りあげたことがありました。

今回は日経系の技術サイトとchipworksからの情報紹介です。

ソニーはここ2年、ISSCCで報告した技術内容を搭載したセンサを、デジタルシネマカメラ搭載撮像素子として、報告より1年以内に世に送り出してきていました。

(2011年:CINEALTAF65搭載、8K高速読み出しセンサ 2012年:CINEALTAF55搭載、グローバルシャッター機能搭載センサ)

”今回はどんな技術が出てくるのかな~?”

とimagerマニアとして楽しみにしていたところ、ちょっと肩透かしで”既に世に製品を公表済みの”センサ技術の報告でした。←いや、他の企業の先をいっているから出来ることであって、凄いことなのですが、まだ聞いたことのない内容を勝手に期待していたので(^^;)

では、上記二つのサイトよりの写真転載と共に以下より。

「」内は例によって私の勝手なプレゼン発言予測です。ご了承を。

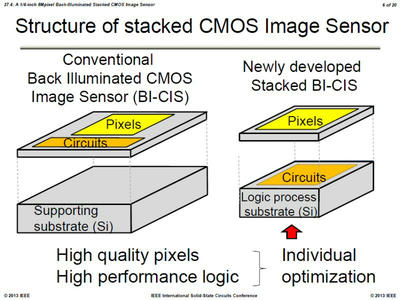

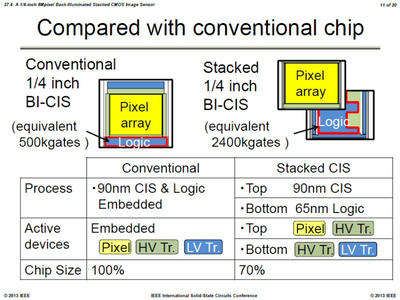

↑ 従来裏面照射センサ(左側)と今回開発した積層型(stacked)センサ(右側)との比較

「従来の裏面センサの支持基板に、Logic回路を移して集積することにより、チップ面積が70%に低減します。

また、top側の画素部とbottom側のLogic回路にそれぞれ最適なプロセスを用いることが可能というメリットがあります。」

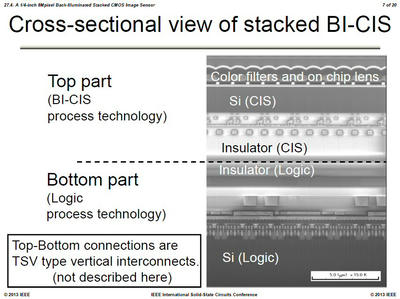

↑ Top側のCMOSイメージセンサプロセス基板(←裏面照射のために研磨して薄くなっている方)とLogic回路が載っている支持基板を積層した断面図

「積層後にtop側とbottom側をSi貫通ビアにて接続します」

※接続された箇所の断面図は、chipworksの写真を後でご紹介します。

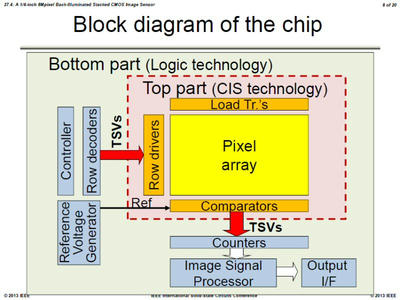

↑top側とbottom側に配置したそれぞれの回路の割り振りとTSVの位置

「”垂直のデコーダとドライバの間”

及び、”列並列に存在するコンパレータ(比較器)と列カウンタの間”でそれぞれtopとbottom基板への配置を分けて、その間をTSVで接続しました。」

「コンパレータまでを画素側のtop基板に配置することにより、(当社の低ノイズ化プロセスをtop基板側に用いることにより)より低ノイズ化が可能です」←元記事より。

※一つ前のエントリで、やはりISSCCで報告されたオリンパスの積層型CMOSを採りあげました。

上記CMOSセンサはグローバルシャッタを効率よく搭載する目的から、画素毎(←4画素ごと)にTSVを用いて積層していました。

しかし、本ソニーのセンサは画素部にはTSVは一切設けず、それぞれ垂直と水平の周辺回路部にて用いるに留めています。

これは、TSVを設ける個数が圧倒的に減ることによる歩留まり低下抑制や、そもそも画素ピッチを狭くして画素数を増やすことに大きく貢献する効率的な積層の仕方だと思います。

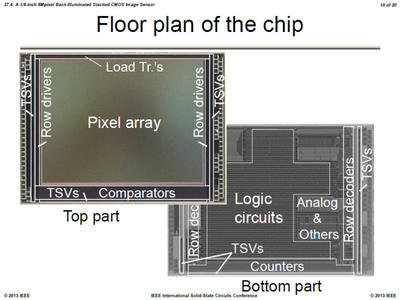

↑実際のチップのフロアプラン図

実際には、一つ前の図と異なり、垂直のデコーダーは左右に設けられていますね。

これは画素ピッチが1.12umと、比較的小さいことから、レイアウト効率を考えて、1行ごとに左右交互にデコーダとドライバを振り分けているのでしょうか。

↑従来CMOSセンサと今回の積層型センサの比較まとめ

「従来型と比較して、積層型(stacked)センサは、bottom側にLogic回路を配置することにより、Logic回路専用の(現状最適な)65nmプロセスを用いることが可能になりました。これにより、(積層型とすることでLogic回路に割り当てる面積がそもそも増えた分と合わせて、)より大きな規模のLogic回路の搭載が可能になりました。更に、Logic回路が搭載されたbottom側は外部のファウンダリに外注することも可能で、当社が常に最先端のLogicプロセスへの投資をする必要が無くなるというメリットもあります。」「また、Logic回路をbottom側へ移すことにより、チップ全体の投影面積は、従来のセンサと比較して70%程度に抑えることが可能になりました。これによりスマホなどの小型携帯機器のカメラモジュールの小型化にも貢献することが可能になります。」

※ここで気になるのは、積層型センサのbottom側にも”HV Tr”の記載がある点です。

(ここでは”HV Tr.=High Voltage transistor","LV Tr.=Low Voltage Transistor"であるはずです。)

直接発表を聞いた訳ではないので、私が意図を汲み違えている可能性が十分ありますが、ここでbottom側にはLV Tr.しかなければ、メリットを素直に頷いて聞けるのですが、HVTr.がbottom側にも存在すると、”結局Bottom側もLogic専用プロセスではなく、電源電圧の異なる混載プロセスが必要になるのじゃないか?”と思ってしまいます。

そもそも何故bottom側に”HV Tr.”が必要だったか?

2枚目の写真で言うところの”Reference Voltage Generater”,3枚目の写真で言うところの”Analog&others”がbottom側にいるからだと思われます。

本発表センサほぼそのままだと思われるソニーセンサのスペックシートを見ると、

電源電圧:digital:1.05V、Analog:2.7V

これはつまり、主にtop側が2.7VのHVTr.で、bottom側が1.05VのLVTr.であるということだと思います。

コンパレータがtop側に配置されていますので、reference voltage generator の最終出力の最大値も2.7V近くまで出力される必要があると思います。それをbottom側で作成しようとすると、1.05VのLVTr.だけでは難しく、結局参照電圧生成器にHVTr.を使用せざると得なくなった。また、もしかししたら”analog&others”の中にtop側で使う1.05V以上の中間電源を生成しているとすると、そのためにもHVTr.は必要になりそうです(←回路によっては中間電源等必要でない可能性もあるので、今回のチップにこの様な中間電源をbottom側で作成しているかは不明ですが)。

では何故”Analog&others”をtop側にもっていかなかったのか?

単純にチップの投影面積の縮小を優先したのでしょうか。

私にはそれぐらいしか思いつきません。

3枚目の写真でanalog&othersはそれなりの面積を持っています。ですので確かにそれをtop側に持っていってしまうと、それなりに面積が増えて、今回の技術のメリットを多少スポイルする方向になってしまいそうです。

まあ、オリジナルのスペックシートを見るとI/Fは1.8~2.9Vとなっており、ここでそもそもHVTr.が必要になりそうです。

このチップ構成ですと、どう考えても出力はbottom側からされるでしょうから、どちらにしてもbottom側にHVTr.が必要になるので、面積効率からanalog&othersもbottom側にするというのは理解できる話だと思います。

ただ、私が理解できないのはI/F電圧はこのチップの都合からすれば、LVTr.でまかなえる程度の低い電圧値でも問題ないように思います。この1.8~2.9Vというのは、スマホなどのシステム設計側の従来製品とのコンパチ性とかの要望でこの様な電圧にしているのでしょうか?←それとも私の知らない出力I/Fの規格等の問題で1.8~2.9Vにせざるを得ないのでしょうか?

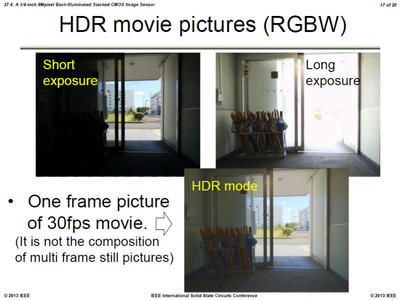

↑本センサチップ単体で画像処理可能になった機能の内の一つの例の紹介。

動画でのHDR(←ハイダイナミックレンジ)機能で撮られた実際の絵

「bottom側に配置した豊富なLogic回路によって、センサチップ単体で実現可能な画像処理の1例として、動画時のHDR機能があります。」「絵を見ていただければ、十分な効果が見て取れると思います。ここで注意していただきたいのは、この動画の絵は”複数枚の絵の合成”によって実現しているわけではなく、あくまで1枚絵で実現しているところです。ですので動画フレームレートも30fpsと、通常の動画モードから落ちません。」

※この動画時のHDRモードの実現方法はこれだと思われます。

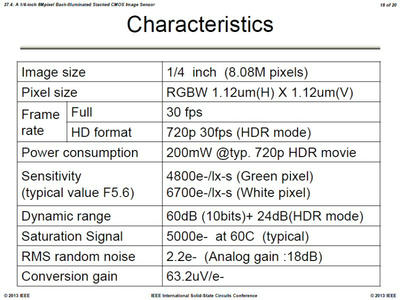

↑本センサの特性まとめ

※見たとおりですが、

まずRGBW画素(white画素)を採用しているところが特徴でしょうか。もちろん感度upを狙ってのことだと思います。

そして画素ピッチの1.12um□。

これは業界最小クラスの画素ピッチです。

また、フレームレートの”Full”が800万画素を指すとすると、スマホとかに搭載されるセンサであることを考えると、相当高速連写可能な部類ではないでしょうか。

感度の値は、普段あまりソニーも含め他社が電子数表示することが少ないので、特性値として凄いのか普通なのかいまひとつ私にはピンときません。しかし、この極小画素ピッチでの話なので恐らく凄い部類なのであろうと思います。

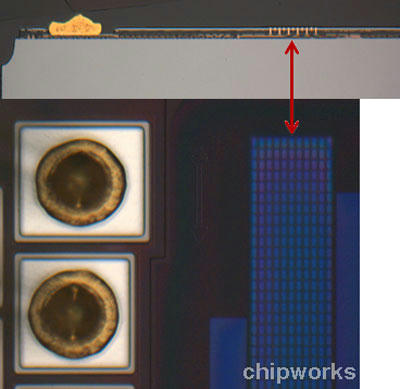

そして以下はchipworksからの写真になります。

↑ 実際にソニーのスマホから取り出したカメラモジュール

”SiP(=System In Package) Here”の文字が(^^;)。

↑ 恐らく、垂直のデコーダ部側のTSV部

chipworksによると、TSVのピッチは6um。

前回のオリンパスの積層型センサが画素部で8umピッチ。

現状の積層型センサの現実的なところはこのくらいのピッチなのでしょう。

TSV部が1列ではなく11列程度になっています。

これは画素ピッチが1.12umでTSVのピッチが6um(←写真では縦のピッチは更に倍の12um程度になっているように見えますが?)。

1列で並べていては必要な穴の数が確保できないために、列数を増やしているのでしょう。

また、どうでも良い話ですが、左側に移っているボンディングパッドの大きさが異なるのが気になりますね。何か意味あるのでしょうか?(^^;)

ソニーの積層型裏面照射センサ(ExmorRS)ネタです。

(ISSCCについてはこちらのエントリの冒頭を参照ください)

以前、ソニーのスマホ搭載の積層型裏面センサの動画HDR(ハイダイナミックレンジ)機能については採りあげたことがありました。

今回は日経系の技術サイトとchipworksからの情報紹介です。

ソニーはここ2年、ISSCCで報告した技術内容を搭載したセンサを、デジタルシネマカメラ搭載撮像素子として、報告より1年以内に世に送り出してきていました。

(2011年:CINEALTAF65搭載、8K高速読み出しセンサ 2012年:CINEALTAF55搭載、グローバルシャッター機能搭載センサ)

”今回はどんな技術が出てくるのかな~?”

とimagerマニアとして楽しみにしていたところ、ちょっと肩透かしで”既に世に製品を公表済みの”センサ技術の報告でした。←いや、他の企業の先をいっているから出来ることであって、凄いことなのですが、まだ聞いたことのない内容を勝手に期待していたので(^^;)

では、上記二つのサイトよりの写真転載と共に以下より。

「」内は例によって私の勝手なプレゼン発言予測です。ご了承を。

↑ 従来裏面照射センサ(左側)と今回開発した積層型(stacked)センサ(右側)との比較

「従来の裏面センサの支持基板に、Logic回路を移して集積することにより、チップ面積が70%に低減します。

また、top側の画素部とbottom側のLogic回路にそれぞれ最適なプロセスを用いることが可能というメリットがあります。」

↑ Top側のCMOSイメージセンサプロセス基板(←裏面照射のために研磨して薄くなっている方)とLogic回路が載っている支持基板を積層した断面図

「積層後にtop側とbottom側をSi貫通ビアにて接続します」

※接続された箇所の断面図は、chipworksの写真を後でご紹介します。

↑top側とbottom側に配置したそれぞれの回路の割り振りとTSVの位置

「”垂直のデコーダとドライバの間”

及び、”列並列に存在するコンパレータ(比較器)と列カウンタの間”でそれぞれtopとbottom基板への配置を分けて、その間をTSVで接続しました。」

「コンパレータまでを画素側のtop基板に配置することにより、(当社の低ノイズ化プロセスをtop基板側に用いることにより)より低ノイズ化が可能です」←元記事より。

※一つ前のエントリで、やはりISSCCで報告されたオリンパスの積層型CMOSを採りあげました。

上記CMOSセンサはグローバルシャッタを効率よく搭載する目的から、画素毎(←4画素ごと)にTSVを用いて積層していました。

しかし、本ソニーのセンサは画素部にはTSVは一切設けず、それぞれ垂直と水平の周辺回路部にて用いるに留めています。

これは、TSVを設ける個数が圧倒的に減ることによる歩留まり低下抑制や、そもそも画素ピッチを狭くして画素数を増やすことに大きく貢献する効率的な積層の仕方だと思います。

↑実際のチップのフロアプラン図

実際には、一つ前の図と異なり、垂直のデコーダーは左右に設けられていますね。

これは画素ピッチが1.12umと、比較的小さいことから、レイアウト効率を考えて、1行ごとに左右交互にデコーダとドライバを振り分けているのでしょうか。

↑従来CMOSセンサと今回の積層型センサの比較まとめ

「従来型と比較して、積層型(stacked)センサは、bottom側にLogic回路を配置することにより、Logic回路専用の(現状最適な)65nmプロセスを用いることが可能になりました。これにより、(積層型とすることでLogic回路に割り当てる面積がそもそも増えた分と合わせて、)より大きな規模のLogic回路の搭載が可能になりました。更に、Logic回路が搭載されたbottom側は外部のファウンダリに外注することも可能で、当社が常に最先端のLogicプロセスへの投資をする必要が無くなるというメリットもあります。」「また、Logic回路をbottom側へ移すことにより、チップ全体の投影面積は、従来のセンサと比較して70%程度に抑えることが可能になりました。これによりスマホなどの小型携帯機器のカメラモジュールの小型化にも貢献することが可能になります。」

※ここで気になるのは、積層型センサのbottom側にも”HV Tr”の記載がある点です。

(ここでは”HV Tr.=High Voltage transistor","LV Tr.=Low Voltage Transistor"であるはずです。)

直接発表を聞いた訳ではないので、私が意図を汲み違えている可能性が十分ありますが、ここでbottom側にはLV Tr.しかなければ、メリットを素直に頷いて聞けるのですが、HVTr.がbottom側にも存在すると、”結局Bottom側もLogic専用プロセスではなく、電源電圧の異なる混載プロセスが必要になるのじゃないか?”と思ってしまいます。

そもそも何故bottom側に”HV Tr.”が必要だったか?

2枚目の写真で言うところの”Reference Voltage Generater”,3枚目の写真で言うところの”Analog&others”がbottom側にいるからだと思われます。

本発表センサほぼそのままだと思われるソニーセンサのスペックシートを見ると、

電源電圧:digital:1.05V、Analog:2.7V

これはつまり、主にtop側が2.7VのHVTr.で、bottom側が1.05VのLVTr.であるということだと思います。

コンパレータがtop側に配置されていますので、reference voltage generator の最終出力の最大値も2.7V近くまで出力される必要があると思います。それをbottom側で作成しようとすると、1.05VのLVTr.だけでは難しく、結局参照電圧生成器にHVTr.を使用せざると得なくなった。また、もしかししたら”analog&others”の中にtop側で使う1.05V以上の中間電源を生成しているとすると、そのためにもHVTr.は必要になりそうです(←回路によっては中間電源等必要でない可能性もあるので、今回のチップにこの様な中間電源をbottom側で作成しているかは不明ですが)。

では何故”Analog&others”をtop側にもっていかなかったのか?

単純にチップの投影面積の縮小を優先したのでしょうか。

私にはそれぐらいしか思いつきません。

3枚目の写真でanalog&othersはそれなりの面積を持っています。ですので確かにそれをtop側に持っていってしまうと、それなりに面積が増えて、今回の技術のメリットを多少スポイルする方向になってしまいそうです。

まあ、オリジナルのスペックシートを見るとI/Fは1.8~2.9Vとなっており、ここでそもそもHVTr.が必要になりそうです。

このチップ構成ですと、どう考えても出力はbottom側からされるでしょうから、どちらにしてもbottom側にHVTr.が必要になるので、面積効率からanalog&othersもbottom側にするというのは理解できる話だと思います。

ただ、私が理解できないのはI/F電圧はこのチップの都合からすれば、LVTr.でまかなえる程度の低い電圧値でも問題ないように思います。この1.8~2.9Vというのは、スマホなどのシステム設計側の従来製品とのコンパチ性とかの要望でこの様な電圧にしているのでしょうか?←それとも私の知らない出力I/Fの規格等の問題で1.8~2.9Vにせざるを得ないのでしょうか?

↑本センサチップ単体で画像処理可能になった機能の内の一つの例の紹介。

動画でのHDR(←ハイダイナミックレンジ)機能で撮られた実際の絵

「bottom側に配置した豊富なLogic回路によって、センサチップ単体で実現可能な画像処理の1例として、動画時のHDR機能があります。」「絵を見ていただければ、十分な効果が見て取れると思います。ここで注意していただきたいのは、この動画の絵は”複数枚の絵の合成”によって実現しているわけではなく、あくまで1枚絵で実現しているところです。ですので動画フレームレートも30fpsと、通常の動画モードから落ちません。」

※この動画時のHDRモードの実現方法はこれだと思われます。

↑本センサの特性まとめ

※見たとおりですが、

まずRGBW画素(white画素)を採用しているところが特徴でしょうか。もちろん感度upを狙ってのことだと思います。

そして画素ピッチの1.12um□。

これは業界最小クラスの画素ピッチです。

また、フレームレートの”Full”が800万画素を指すとすると、スマホとかに搭載されるセンサであることを考えると、相当高速連写可能な部類ではないでしょうか。

感度の値は、普段あまりソニーも含め他社が電子数表示することが少ないので、特性値として凄いのか普通なのかいまひとつ私にはピンときません。しかし、この極小画素ピッチでの話なので恐らく凄い部類なのであろうと思います。

そして以下はchipworksからの写真になります。

↑ 実際にソニーのスマホから取り出したカメラモジュール

”SiP(=System In Package) Here”の文字が(^^;)。

↑ 恐らく、垂直のデコーダ部側のTSV部

chipworksによると、TSVのピッチは6um。

前回のオリンパスの積層型センサが画素部で8umピッチ。

現状の積層型センサの現実的なところはこのくらいのピッチなのでしょう。

TSV部が1列ではなく11列程度になっています。

これは画素ピッチが1.12umでTSVのピッチが6um(←写真では縦のピッチは更に倍の12um程度になっているように見えますが?)。

1列で並べていては必要な穴の数が確保できないために、列数を増やしているのでしょう。

また、どうでも良い話ですが、左側に移っているボンディングパッドの大きさが異なるのが気になりますね。何か意味あるのでしょうか?(^^;)

オリンパス グローバルシャッター搭載の積層型CMOS開発 ~このセンサのFabもソニー??

ISSCCというのをご存知でしょうか?

毎年2月に米国はサンフランシスコで開催される”半導体回路のオリンピック”と呼ばれる国際会議です。

正式名称は”International Solid-State Circuits Conference”(国際固体素子回路会議)で、採択率は3割前後という超難関。

加えてもう一つ、”動作する実物を作っていないと発表する権利がない”という大きな特徴があります。

つまり、理論上可能かどうか怪しいタイムマシンについては勿論のこと、理屈上は可能なことが十分立証されている短期的未来に作製可能なものであったとしても”モノ”が無いと採択されることはありません。

過去にはこんなソニーの超高速読み出しのデジタル出力センサが発表されましたし、今年もソニーやパナソニックからも報告があり、センサ分野で全9件の発表中、日本勢が半数以上の5件を占めるという”日本電機業界最後の砦”を地で行く強さです(^^)。

さて、前置きが長くなりました。

今回は、そんなISSCCから、オリンパスが報告したセンサ(撮像素子/CMOSイメージセンサ/imager)を採り挙げてみたいと思います。

オリンパスは今回、”グローバルシャッター搭載の積層型CMOSセンサ” を報告しました。

しかしながら、結論を先に書きますと、私の誤解が無ければ、完全なグローバルシャッターではないようです。

それでも十分凄い技術ではありますが・・・。

では以下より具体的に。写真は基本上記サイトからの転載となります。

尚、「」内は、私が勝手に資料内容から”こんな説明内容だったんだろうな”という完全な憶測で付記しています(^^;)

ご了承を。

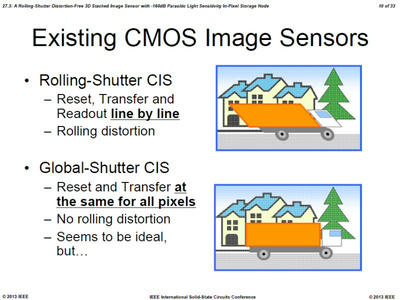

↑ 発表資料をそのまま写真に収めたものと思われます。

恐らく導入部分。「CMOSセンサには元来動体撮影するとローリングシャッター歪みが出ます。グローバルシャッターなら歪みは出ません。何故ならフォトダイオードを全画素同時にリセットして読み出すからです。しかし弱点があります・・・」

う~ん、ISSCCを聴講しにくる様な人にこの説明必要なのか?(^^;)

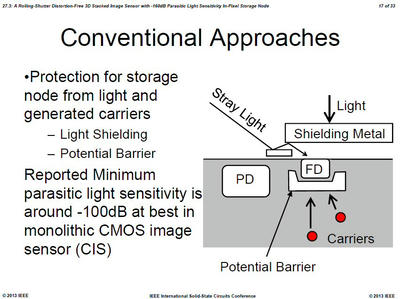

↑ 「従来のグローバルシャッターセンサーは、一時電荷保持容量であるFDを、入射光から守るために遮光したり、またシリコン中からの発生電荷を拾ってしまわないように、ポテンシャルバリアを設けたりしていました。しかし、この様な方式では、過去最小でも-100dB(←入射光に対して10万分の1程度の感度を保持部であるFDが持ってしまっていて、それが次フレームの残像になっていた)程度でした。」

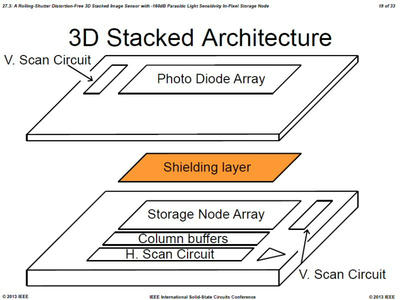

↑ 「そこで今回当社では、フォトダイオードへの入射光から一時電荷保持容量への漏れ光を完全に無くすために、3次元積層構造を採用し、電荷保持容量部をフォトダイオードとは異なる積層レイヤに配置させ、更に積層間に遮光層を設けることにしました」

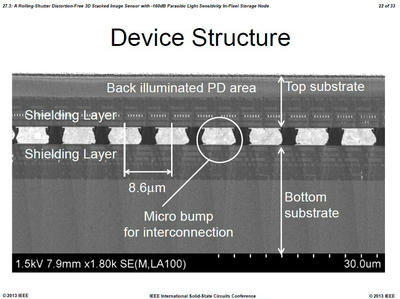

↑「積層構造にするために、上下層を電気的に導通させる必要があり、この写真の様なマイクロバンプを用いて接続しています。バンプ間のピッチは8.6um。直径5um。高さ4umとなっています。」

※5umと4umという数字は元記事より。

また、今回のセンサの画素ピッチは4.3umとなっているようです。

つまり、8.6umというバンプのピッチでは4画素に一つしか、独立した導通を上下レイヤで持つことが出来ません。

そのため、次の等価回路図に出てきますが、4画素でFD部を共有する回路構成となっているようです。

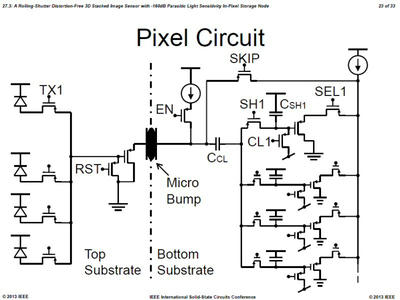

↑ 「画素部の等価回路図です。4画素でFDやSF、リセットトランジスタを共有しています。top基板側にフォトダイオードと転送、リセット、SFトランジスタ、及びFD部を配置。bottom基板側にグローバルシャッタ動作に必要な一時電荷保持容量部を作りこみました。上下の基板のつなぎ目は画素ソースフォロワの出力ノードをマイクロバンプでつないでいます。」

※後で、この等価回路図で予想されるグローバルシャッタ読み時の駆動タイミングを示しますが、上記等価回路を一瞥してすぐに、残念ながら”4画素同時に読むには加算以外に方法がない=上記セットの4画素に関しては、完全にグローバルシャッターを実現出来ていない”ということがわかります。

何故なら、FD及び画素ソースフォロワが4画素に一つしかないため、グローバルシャッタの”全画素同時リセット及び読み出し”の読み出し側が、同時に行うとどうしても加算になってしまうからです。

恐らく、現状の技術では、まだ4.3umピッチでマイクロバンプで上下レイヤをつなぐことが歩留まり良く出来ないのではないでしょうか。

そのための画素ピッチの丁度倍の8.6umピッチでつなぐことにして、回路は仕方なく4画素共有としたと。

※オリジナル記事の方には、「マイクロバンプの接続の歩留まりは99.9%以上」という信じられないくらいの高い数字が載っています。

この数字を信じるならば、もう少し技術革新すれば、4.3umピッチのバンプ作製も99.9%とは言わないまでも量産可能なレベルにまで引き上げられる可能性は十分ありそうですね。

ちなみに、本回路の駆動を考えるに、等価回路図の”SKIP”は、グローバルシャッタを行わずに従来のローリングシャッタ読みをする際にのみONするスイッチで、ENは逆にグローバルシャッタ読みをする時のみONするスイッチではないかと思います。

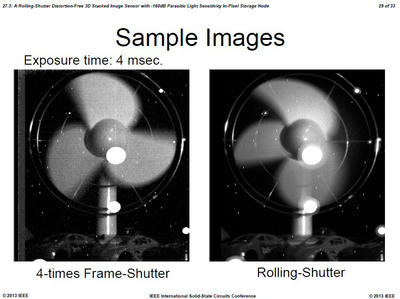

↑ 「実際に本センサで撮影した写真が左になります。右が比較のために従来のローリングシャッタCMOSセンサで撮影したものです。本センサで見事にローリングシャッタ歪みがなくなっているのがお分かりいただけると思います。」

この写真の左側の注釈”4-times Frame-shutter”とはどういう意味でしょうか?

4画素でFD共通のため、4回読み出さないと全画素の絵が取得できないから、4フレーム分読み出したものをエンジンで合成したもの という様な意味でしょうか?

最後のプレゼン資料に出てくる”30fps”は、この4フレーム分を1fpsとカウントした場合のフレームレートなのでしょうか?それとも全画素読み出すには30/4fpsのフレームレートになってしまうのでしょうか?

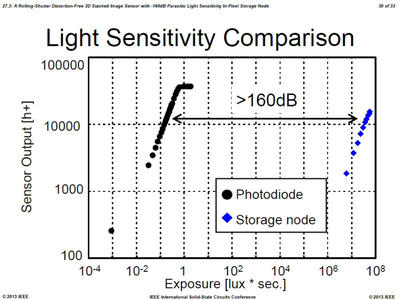

↑ 「本センサのフォトダイオードと電荷保持容量部の感度特性差です。

top基板側にあるフォトダイオードと160dB以上の差が確保されていることがわかります。」

※これは横軸はtop層側から入射させた光量(ルクス×秒)。つまり見方としては、きちんと遮光されたボトム基板側の電荷保持容量部が出す出力は、フォトダイオードと同じ出力を出さそうと思ったら、1億倍の光量を当てなければならず、逆に同じ光量をあてた場合には、フォトダイオードに対して(1/1億)しか出力を出さない≒つまり電荷保持容量部で発生してしまうノイズ(残像)成分は信号に対して(1/1億)しかない良い特性ですよ ということ。

しかし、逆に興味深いのは、ボトム基板側に配置して、かつ間にシールド層を入れたにも関わらず、(1/1億)とはいえ感度を持ってしまうこと(^^;)。いや、「問題となるレベルではない」というご意見には同意します。単に「それでもわずかながら光が届いてしまうんだ」という驚きです。

また、そもそも”従来センサの-100dB”という遮光能力では問題なのでしょうか?

次ページのプレゼン資料で、このセンサの飽和ホール数が30000ホール以上であることが示されます。

仮に飽和の30倍の光量がフォトダイオード面に当たったとして90万ホール。これの10万分の1しか保持容量にホール蓄積されないのだとすると、それでも9ホール程度しか出てこない計算です。

う~ん、断言は出来ませんが、これは太陽か、夜の車のヘッドライトでも撮らない限りは事実上問題ないのでは?

まあ従来センサが本当に-100dBの遮光性能があったかは逆に疑問ですが(^^;)

↑ 書いてからよくよく考えると、前提はメカのシャッターの無いシステムへの組み込みを想定しているセンサの話でしょうから、従来センサの最後に読み出される行は適切な露光量の調節もなく、1フレームの読み出し時間程度光があたりっぱなし。また、そもそもこの課題においてフォトダイオードの飽和がいくらかは本質的には関係ない。

そう考えると、何だかやっぱり-100dB程度では通常使用においても問題が出るような気がしてきました(^^;)

これだとやっぱり

このセンサの電源電圧が何Vなのか不明なため、なんとも言えませんが、3.3Vかもしくは2.8V程度と予想すると、むしろその電源電圧においてグローバルシャッタを実現した上で30000ホールの飽和を確保しているということの方が偉業の様に感じてしまいます。←当然これは積層型にしてフォトダイオードとは別の場所に電荷保持容量を形成できたため、フォトダイオードの面積を圧迫しなくて済んだ恩恵であろうと予想します。

こっちをもっと大々的にアピールした方がいいんじゃないかな?

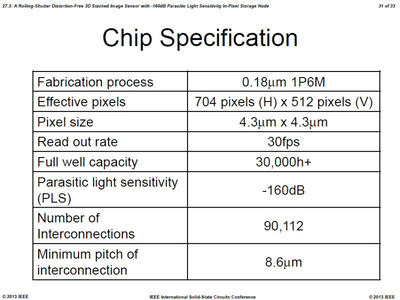

↑ 「最後に本センサのスペックまとめです。」

やっぱり、積層型ともなると6層メタル配線くらい必要になるのですね。この内グローバルシャッターとして増加してしまった分は何メタル分なのでしょうか?

どちらにしても、配線層の増加とそもそも積層型とすることで、かなりなコスト高にはなりそう・・・・・・なのですが、

ソニーは積層型センサを最もコスト競争力が必要そうなスマホ向けに量産しています。

ソニー曰く「top層にはセンサに最適なプロセスを、ボトム側にはロジックに最適なプロセスを それぞれ用いて作製した基板を張り合わせるので、双方を一つの基板に形成するよりも歩留まりが良い」のだとか。

今回のオリンパスのは、この構成だとボトム基板側にもアナログ回路が存在するはずなので、上記と同じ理屈は成り立ちませんが、実際のところは如何なものなのでしょうか?

また、画素数は704×512≒36万画素 程度なので、まだまだ完全に試作レベルですね。←監視カメラ程度なら使える画素数かもしれませんが、監視カメラにわざわざグローバルシャッタセンサを意地で投入する必要はなさそうですし(^^;)。

4.3umピッチでそのままフォーサーズサイズまで引き伸ばせば1200万画素少々ということで、最近のフォーサーズが1600万画素台が主流なので、グローバルシャッター機能を全面に押し出せば、ギリギリ商品性がある画素数のセンサになるように思います。

そこまで考えての開発でしょうか?←期待したいです。

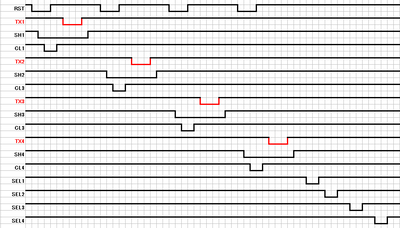

↑ 最後に私が勝手に作成した、このオリンパスセンサのグローバルシャッタ駆動時のタイミングチャートです。

上の等価回路図を合わせてご覧ください。

注!!)このセンサは等価回路図を見ると、どうもホール蓄積型で、画素MOSは全てpMOSで形成されているようです。

そのため、ゲートパルスの極性として、Low=Activeで上記タイミングチャートは記載しています。

細かいところは異なるかもしれませんが、概略動作として合っているのではないかと思っています。

詳細の説明は省きますが、ここで着目したいのは、グローバルシャッタとして重要なフォトダイオードの同時リセットは可能ですが、赤い転送パルス部分が、どうしても4画素同時には出来そうもありません。

注) このチャートの横軸は時間(t)です。

最後になりますが、最大の興味がある疑問を。

”このセンサを作っているFabはどこか?”

ちなみにオリンパスはFabレス会社です。つまり自社で設計はしますが、半導体工場は持っていないため、どこかに依頼しないとセンサ製造自体はムリです。

まともに考えると簡単な消去法でソニーが浮かびそうです。

こんな積層型センサなんて、マニアックな凄いものを、そうそう簡単にいくつものメーカーが作れるようになる気がしませんから・・・・・・

しかし、裏面照射型センサは、あっという間に今や複数の会社が量産していますので、もしかしたらこの積層型センサもソニー製でない可能性も!!??

毎年2月に米国はサンフランシスコで開催される”半導体回路のオリンピック”と呼ばれる国際会議です。

正式名称は”International Solid-State Circuits Conference”(国際固体素子回路会議)で、採択率は3割前後という超難関。

加えてもう一つ、”動作する実物を作っていないと発表する権利がない”という大きな特徴があります。

つまり、理論上可能かどうか怪しいタイムマシンについては勿論のこと、理屈上は可能なことが十分立証されている短期的未来に作製可能なものであったとしても”モノ”が無いと採択されることはありません。

過去にはこんなソニーの超高速読み出しのデジタル出力センサが発表されましたし、今年もソニーやパナソニックからも報告があり、センサ分野で全9件の発表中、日本勢が半数以上の5件を占めるという”日本電機業界最後の砦”を地で行く強さです(^^)。

さて、前置きが長くなりました。

今回は、そんなISSCCから、オリンパスが報告したセンサ(撮像素子/CMOSイメージセンサ/imager)を採り挙げてみたいと思います。

オリンパスは今回、”グローバルシャッター搭載の積層型CMOSセンサ” を報告しました。

しかしながら、結論を先に書きますと、私の誤解が無ければ、完全なグローバルシャッターではないようです。

それでも十分凄い技術ではありますが・・・。

では以下より具体的に。写真は基本上記サイトからの転載となります。

尚、「」内は、私が勝手に資料内容から”こんな説明内容だったんだろうな”という完全な憶測で付記しています(^^;)

ご了承を。

↑ 発表資料をそのまま写真に収めたものと思われます。

恐らく導入部分。「CMOSセンサには元来動体撮影するとローリングシャッター歪みが出ます。グローバルシャッターなら歪みは出ません。何故ならフォトダイオードを全画素同時にリセットして読み出すからです。しかし弱点があります・・・」

う~ん、ISSCCを聴講しにくる様な人にこの説明必要なのか?(^^;)

↑ 「従来のグローバルシャッターセンサーは、一時電荷保持容量であるFDを、入射光から守るために遮光したり、またシリコン中からの発生電荷を拾ってしまわないように、ポテンシャルバリアを設けたりしていました。しかし、この様な方式では、過去最小でも-100dB(←入射光に対して10万分の1程度の感度を保持部であるFDが持ってしまっていて、それが次フレームの残像になっていた)程度でした。」

↑ 「そこで今回当社では、フォトダイオードへの入射光から一時電荷保持容量への漏れ光を完全に無くすために、3次元積層構造を採用し、電荷保持容量部をフォトダイオードとは異なる積層レイヤに配置させ、更に積層間に遮光層を設けることにしました」

↑「積層構造にするために、上下層を電気的に導通させる必要があり、この写真の様なマイクロバンプを用いて接続しています。バンプ間のピッチは8.6um。直径5um。高さ4umとなっています。」

※5umと4umという数字は元記事より。

また、今回のセンサの画素ピッチは4.3umとなっているようです。

つまり、8.6umというバンプのピッチでは4画素に一つしか、独立した導通を上下レイヤで持つことが出来ません。

そのため、次の等価回路図に出てきますが、4画素でFD部を共有する回路構成となっているようです。

↑ 「画素部の等価回路図です。4画素でFDやSF、リセットトランジスタを共有しています。top基板側にフォトダイオードと転送、リセット、SFトランジスタ、及びFD部を配置。bottom基板側にグローバルシャッタ動作に必要な一時電荷保持容量部を作りこみました。上下の基板のつなぎ目は画素ソースフォロワの出力ノードをマイクロバンプでつないでいます。」

※後で、この等価回路図で予想されるグローバルシャッタ読み時の駆動タイミングを示しますが、上記等価回路を一瞥してすぐに、残念ながら”4画素同時に読むには加算以外に方法がない=上記セットの4画素に関しては、完全にグローバルシャッターを実現出来ていない”ということがわかります。

何故なら、FD及び画素ソースフォロワが4画素に一つしかないため、グローバルシャッタの”全画素同時リセット及び読み出し”の読み出し側が、同時に行うとどうしても加算になってしまうからです。

恐らく、現状の技術では、まだ4.3umピッチでマイクロバンプで上下レイヤをつなぐことが歩留まり良く出来ないのではないでしょうか。

そのための画素ピッチの丁度倍の8.6umピッチでつなぐことにして、回路は仕方なく4画素共有としたと。

※オリジナル記事の方には、「マイクロバンプの接続の歩留まりは99.9%以上」という信じられないくらいの高い数字が載っています。

この数字を信じるならば、もう少し技術革新すれば、4.3umピッチのバンプ作製も99.9%とは言わないまでも量産可能なレベルにまで引き上げられる可能性は十分ありそうですね。

ちなみに、本回路の駆動を考えるに、等価回路図の”SKIP”は、グローバルシャッタを行わずに従来のローリングシャッタ読みをする際にのみONするスイッチで、ENは逆にグローバルシャッタ読みをする時のみONするスイッチではないかと思います。

↑ 「実際に本センサで撮影した写真が左になります。右が比較のために従来のローリングシャッタCMOSセンサで撮影したものです。本センサで見事にローリングシャッタ歪みがなくなっているのがお分かりいただけると思います。」

この写真の左側の注釈”4-times Frame-shutter”とはどういう意味でしょうか?

4画素でFD共通のため、4回読み出さないと全画素の絵が取得できないから、4フレーム分読み出したものをエンジンで合成したもの という様な意味でしょうか?

最後のプレゼン資料に出てくる”30fps”は、この4フレーム分を1fpsとカウントした場合のフレームレートなのでしょうか?それとも全画素読み出すには30/4fpsのフレームレートになってしまうのでしょうか?

↑ 「本センサのフォトダイオードと電荷保持容量部の感度特性差です。

top基板側にあるフォトダイオードと160dB以上の差が確保されていることがわかります。」

※これは横軸はtop層側から入射させた光量(ルクス×秒)。つまり見方としては、きちんと遮光されたボトム基板側の電荷保持容量部が出す出力は、フォトダイオードと同じ出力を出さそうと思ったら、1億倍の光量を当てなければならず、逆に同じ光量をあてた場合には、フォトダイオードに対して(1/1億)しか出力を出さない≒つまり電荷保持容量部で発生してしまうノイズ(残像)成分は信号に対して(1/1億)しかない良い特性ですよ ということ。

しかし、逆に興味深いのは、ボトム基板側に配置して、かつ間にシールド層を入れたにも関わらず、(1/1億)とはいえ感度を持ってしまうこと(^^;)。いや、「問題となるレベルではない」というご意見には同意します。単に「それでもわずかながら光が届いてしまうんだ」という驚きです。

次ページのプレゼン資料で、このセンサの飽和ホール数が30000ホール以上であることが示されます。

仮に飽和の30倍の光量がフォトダイオード面に当たったとして90万ホール。これの10万分の1しか保持容量にホール蓄積されないのだとすると、それでも9ホール程度しか出てこない計算です。

う~ん、断言は出来ませんが、これは太陽か、夜の車のヘッドライトでも撮らない限りは事実上問題ないのでは?

まあ従来センサが本当に-100dBの遮光性能があったかは逆に疑問ですが(^^;)

↑ 書いてからよくよく考えると、前提はメカのシャッターの無いシステムへの組み込みを想定しているセンサの話でしょうから、従来センサの最後に読み出される行は適切な露光量の調節もなく、1フレームの読み出し時間程度光があたりっぱなし。また、そもそもこの課題においてフォトダイオードの飽和がいくらかは本質的には関係ない。

そう考えると、何だかやっぱり-100dB程度では通常使用においても問題が出るような気がしてきました(^^;)

これだとやっぱり

このセンサの電源電圧が何Vなのか不明なため、なんとも言えませんが、3.3Vかもしくは2.8V程度と予想すると、むしろその電源電圧においてグローバルシャッタを実現した上で30000ホールの飽和を確保しているということの方が偉業の様に感じてしまいます。←当然これは積層型にしてフォトダイオードとは別の場所に電荷保持容量を形成できたため、フォトダイオードの面積を圧迫しなくて済んだ恩恵であろうと予想します。

こっちをもっと大々的にアピールした方がいいんじゃないかな?

↑ 「最後に本センサのスペックまとめです。」

やっぱり、積層型ともなると6層メタル配線くらい必要になるのですね。この内グローバルシャッターとして増加してしまった分は何メタル分なのでしょうか?

どちらにしても、配線層の増加とそもそも積層型とすることで、かなりなコスト高にはなりそう・・・・・・なのですが、

ソニーは積層型センサを最もコスト競争力が必要そうなスマホ向けに量産しています。

ソニー曰く「top層にはセンサに最適なプロセスを、ボトム側にはロジックに最適なプロセスを それぞれ用いて作製した基板を張り合わせるので、双方を一つの基板に形成するよりも歩留まりが良い」のだとか。

今回のオリンパスのは、この構成だとボトム基板側にもアナログ回路が存在するはずなので、上記と同じ理屈は成り立ちませんが、実際のところは如何なものなのでしょうか?

また、画素数は704×512≒36万画素 程度なので、まだまだ完全に試作レベルですね。←監視カメラ程度なら使える画素数かもしれませんが、監視カメラにわざわざグローバルシャッタセンサを意地で投入する必要はなさそうですし(^^;)。

4.3umピッチでそのままフォーサーズサイズまで引き伸ばせば1200万画素少々ということで、最近のフォーサーズが1600万画素台が主流なので、グローバルシャッター機能を全面に押し出せば、ギリギリ商品性がある画素数のセンサになるように思います。

そこまで考えての開発でしょうか?←期待したいです。

↑ 最後に私が勝手に作成した、このオリンパスセンサのグローバルシャッタ駆動時のタイミングチャートです。

上の等価回路図を合わせてご覧ください。

注!!)このセンサは等価回路図を見ると、どうもホール蓄積型で、画素MOSは全てpMOSで形成されているようです。

そのため、ゲートパルスの極性として、Low=Activeで上記タイミングチャートは記載しています。

細かいところは異なるかもしれませんが、概略動作として合っているのではないかと思っています。

詳細の説明は省きますが、ここで着目したいのは、グローバルシャッタとして重要なフォトダイオードの同時リセットは可能ですが、赤い転送パルス部分が、どうしても4画素同時には出来そうもありません。

注) このチャートの横軸は時間(t)です。

最後になりますが、最大の興味がある疑問を。

”このセンサを作っているFabはどこか?”

ちなみにオリンパスはFabレス会社です。つまり自社で設計はしますが、半導体工場は持っていないため、どこかに依頼しないとセンサ製造自体はムリです。

まともに考えると簡単な消去法でソニーが浮かびそうです。

こんな積層型センサなんて、マニアックな凄いものを、そうそう簡単にいくつものメーカーが作れるようになる気がしませんから・・・・・・

しかし、裏面照射型センサは、あっという間に今や複数の会社が量産していますので、もしかしたらこの積層型センサもソニー製でない可能性も!!??

CP+ 2013レポート ~ペンタックス リコーイメージング ブース

時間が経ってしまっていますが、今月初旬のCP+を自分の備忘録として残しておきたいと思います。

以前のエントリで、フジの”フジがき隊”とソニーブースを書きましたが、今回は好印象ブースだった内の一つペンタックスリコーイメージングブースです。

余談ですが、ペンタックスは以前HOYAという光学ガラスメーカーに買い取られ、しかし儲けを出している医療機関係部門だけ切り取られ、HOYAでカメラ部門はお荷物の様に扱われていました。

その後、カメラ部門だけリコーが買い取っています。

今回のリコーよりもペンタックスブランドの方が大きく扱われているCP+のブースを見て、「本当にカメラに理解がある会社に買い取られて良かったな」と安堵しました。

当時、下手を打つとサムスンとかに売られて、また日本の貴重な技術が韓国に流れるのではないかと心配したものです。

上記事件(!?)のお陰で、私の中でHOYAの企業イメージが下がり、リコーの企業イメージがupしたことは言う間でもありません(笑)

では、以下より写真レポートを。

↑ ”PENTAX”の方が大きく扱われているブース玄関

↑ ペンタックスお得意、完全受注生産の”100色カラバリ”

グリップとのデザインの組み合わせ変更とかも可能

↑リコー GR DIGITALの4世代目

根強い人気のブランド

↑ 超マニアの間から要望の強かった”イメージセンサ交換式”カメラ(実際には撮像素子とレンズマウントとレンズ自身を一緒に交換する)を実現したリコー GXRシリーズ

↑ ペンタックス 645D (←中判カメラ。撮像素子は44×33mmのイメージ領域を持つCCD) と 645マウントのレンズ群

ペンタックスリコーの凄いところは、上のGXRといい、この645Dと言い(全く私の予測でしかありませんが、恐らくのところ)商売上は成り立っていない(←つまり単体では儲けは出ていないであろう(^^;))カメラを発売して、かつそれを続けていることだと思うのです。

上記予測が当たっていれば、”最早ユーザーのためだけに”生産し続けているということになります(←ブランドイメージのためというのもあるかもしれませんが)。

(仕方がないとは思いますが)オリンパスのフォーサーズマウントのカメラとレンズが事実上の開発凍結状態であるのと対照的だなと、個人的に感じています。

また、ラインナップとして、APS-Cサイズの一眼レフのKシリーズ、中判サイズの645マウントを持っているのに、間のフルサイズ(36×24mm)の製品群を持たないというのもおもしろい。意図してか、偶然か?

今回のCP+で、ペンタックスが「フルサイズも出すべきだと考えている」とインタビューに答えているので、そのうちフルサイズもラインナップに加わるかもしれませんね。

↑ そして今回の目玉(!?)がこれ!!!

脅威の(!?)”Qだけ”つながり!エヴァQとペンタックスQ10コラボ

実物大等身フィギュアを用意し、カメラは左から綾波レイ、エヴァ初号機、アスカ の3モデルを用意。パッケージの箱もオリジナル。ネルフの文字も。

限定生産もので、既に完売御礼。

何というか、100色カラーバリエーションやこのQコラボに、会社の余裕というか悪ノリというか ”やわらかい”良い雰囲気を勝手に感じてしまいます(^^;)。

↑ そして、そのQマウントレンズラインナップ(右)と、Kマウントラインナップ(左)

Kマウントはレンズもカラバリ仕様(^^;)

しかし、ペンタックスリコーは、キヤノン、ニコン、ソニー、パナ等と比較すると会社の規模は大きくないのに、

645マウント、Kマウント(一眼レフとミラーレス双方)、Qマウント、それにGRX(←これはマウントじゃないけれど)と、豊富なマウントと製品群を持っています。

ユーザーにとっては、ラインナップが多いことは選択肢を増やすので何かと嬉しい方向だと思うのですが、ちょっと老婆心ながら心配になってしまいます(^^;)。

以前のエントリで、フジの”フジがき隊”とソニーブースを書きましたが、今回は好印象ブースだった内の一つペンタックスリコーイメージングブースです。

余談ですが、ペンタックスは以前HOYAという光学ガラスメーカーに買い取られ、しかし儲けを出している医療機関係部門だけ切り取られ、HOYAでカメラ部門はお荷物の様に扱われていました。

その後、カメラ部門だけリコーが買い取っています。

今回のリコーよりもペンタックスブランドの方が大きく扱われているCP+のブースを見て、「本当にカメラに理解がある会社に買い取られて良かったな」と安堵しました。

当時、下手を打つとサムスンとかに売られて、また日本の貴重な技術が韓国に流れるのではないかと心配したものです。

上記事件(!?)のお陰で、私の中でHOYAの企業イメージが下がり、リコーの企業イメージがupしたことは言う間でもありません(笑)

では、以下より写真レポートを。

↑ ”PENTAX”の方が大きく扱われているブース玄関

↑ ペンタックスお得意、完全受注生産の”100色カラバリ”

グリップとのデザインの組み合わせ変更とかも可能

↑リコー GR DIGITALの4世代目

根強い人気のブランド

↑ 超マニアの間から要望の強かった”イメージセンサ交換式”カメラ(実際には撮像素子とレンズマウントとレンズ自身を一緒に交換する)を実現したリコー GXRシリーズ

↑ ペンタックス 645D (←中判カメラ。撮像素子は44×33mmのイメージ領域を持つCCD) と 645マウントのレンズ群

ペンタックスリコーの凄いところは、上のGXRといい、この645Dと言い(全く私の予測でしかありませんが、恐らくのところ)商売上は成り立っていない(←つまり単体では儲けは出ていないであろう(^^;))カメラを発売して、かつそれを続けていることだと思うのです。

上記予測が当たっていれば、”最早ユーザーのためだけに”生産し続けているということになります(←ブランドイメージのためというのもあるかもしれませんが)。

(仕方がないとは思いますが)オリンパスのフォーサーズマウントのカメラとレンズが事実上の開発凍結状態であるのと対照的だなと、個人的に感じています。

また、ラインナップとして、APS-Cサイズの一眼レフのKシリーズ、中判サイズの645マウントを持っているのに、間のフルサイズ(36×24mm)の製品群を持たないというのもおもしろい。意図してか、偶然か?

今回のCP+で、ペンタックスが「フルサイズも出すべきだと考えている」とインタビューに答えているので、そのうちフルサイズもラインナップに加わるかもしれませんね。

↑ そして今回の目玉(!?)がこれ!!!

脅威の(!?)”Qだけ”つながり!エヴァQとペンタックスQ10コラボ

実物大等身フィギュアを用意し、カメラは左から綾波レイ、エヴァ初号機、アスカ の3モデルを用意。パッケージの箱もオリジナル。ネルフの文字も。

限定生産もので、既に完売御礼。

何というか、100色カラーバリエーションやこのQコラボに、会社の余裕というか悪ノリというか ”やわらかい”良い雰囲気を勝手に感じてしまいます(^^;)。

↑ そして、そのQマウントレンズラインナップ(右)と、Kマウントラインナップ(左)

Kマウントはレンズもカラバリ仕様(^^;)

しかし、ペンタックスリコーは、キヤノン、ニコン、ソニー、パナ等と比較すると会社の規模は大きくないのに、

645マウント、Kマウント(一眼レフとミラーレス双方)、Qマウント、それにGRX(←これはマウントじゃないけれど)と、豊富なマウントと製品群を持っています。

ユーザーにとっては、ラインナップが多いことは選択肢を増やすので何かと嬉しい方向だと思うのですが、ちょっと老婆心ながら心配になってしまいます(^^;)。

ニコンD7100搭載センサも東芝製・・・・・・ で、間違いないように見えます ~今後も東芝APS-Cサイズセンサは増えそうな予感

↑ ニコンHPにupされていた、本日発表の一眼レフデジカメD7100搭載、APS-Cサイズimager(撮像素子)の写真

本日、ニコンからD7100という、現状APS-Cサイズのニコン機のフラグシップとなるカメラが発表されました。

何でも真のローパスレスモデルだそうで(D800Eは実は光学ローパスは存在していたが、お互いが効果を打ち消しあうように間に入っていた”波長板”というのを単なるガラスに置き換えられていた)、ペンタックスのK-5ⅡsやフジのX-Pro1に続くものになります。

最近ニコンはデジタル一眼レフの発売ペースが早いような?元気がありますね。

さて、ニコンD5200は既に東芝製のセンサが搭載されていることがわかっていますが、今回のD7100もどうやら同じ東芝製のセンサの様に見えます。

以前、ニコンの最近の一眼レフカメラ搭載撮像素子の写真を並べてみましたが、このD5200の写真と同じものに見えるからです。

D5200とD7100の有効画素数も2410万画素で同じですし、撮像素子のサイズも23.5mmx15.6mmで同じですし、なによりあの偏ったパッケージに対するセンサの実装位置といい(笑)、センサの画素領域上下の周辺回路の偏りといい、間違いない様に思います。

駒速が6駒と5駒で異なりますが、これはD5200の方をハード的に抑えているのでしょうし、D7100の対DX1.3倍クロップもファームウェアと画像処理エンジンで差をつけているのでしょう。

しかし随分と急速にニコンと東芝が仲良くなったものです。

まあ、パッケージを一度作ると金型代も馬鹿にならないと思われるので、パッケージを含めた実装を一切D5200から変更せずに東芝はニコンに対してセンサを供給しているのでしょう。ニコン2台分のカメラに対する売り上げで、新規開発センサの元を取って更に儲けると。

そして、ニコンのカメラ組み立て工場の方で、ローパスフィルタの有無も含めてD5200とD7100に組み分けると。

今回、東芝はAPS-Cサイズセンサ製造は初めてだったと思うので、半導体工程、検査工程、パッケージ実装工程と色んなところに新規の設備投資を行わざるを得なかったでしょう。なので、実際は今回のこのセンサだけでは元は取れないのではないかと思います。

つまり何が言いたいのかというと、今後もニコン及びその他の会社に対して積極的にAPS-Cサイズセンサを売り込むと思うので、今後も一眼レフカメラに東芝製のセンサが搭載されることが多くなるのではないでしょうか。

ブログ内検索

カウンター

最新コメント

[03/28 hoge]

[03/26 hi-low]

[03/22 山川]

[03/18 hoge]

[03/08 hi-low]

[03/04 hoge]

[02/26 山川]

[02/26 山川]

[02/19 hoge]

[02/18 山川]

[02/05 hoge]

[02/05 hi-low]

[01/29 通りすがりです]

[01/28 FT]

[01/23 hi-low]

カテゴリー

カレンダー

最新記事

(04/22)

(04/01)

(03/25)

(03/17)

(03/11)

最古記事

プロフィール

HN:

imagerマニア

性別:

非公開