Imager マニア

デジカメ / デジタルビデオカメラ / スマホ用の撮像素子(イメージセンサ/imager/CMOSセンサ)について、マニアな情報や私見を徒然なるままに述べるBlogです(^^;)

[PR]

×

[PR]上記の広告は3ヶ月以上新規記事投稿のないブログに表示されています。新しい記事を書く事で広告が消えます。

ソニーの次期センサは画素毎に積層bottom基板とコンタクト? ~Ziptronix社との特許契約から

今回は、先々週までのISSCCネタから少し離れて、いつも情報源として(勝手に)お世話になっているコチラのサイトのニュースから。

しばらく前、上記サイトで、ソニーがZiptronixという聞きなれない会社から、新たに積層型センサのためのウェハ貼り合わせの特許ライセンス契約を結んだという様な内容のニュースを読んでいました。

(あくまで、上記情報をオープンにしたのはZiptronix社であって、ソニーがわざわざオープンにしている情報ではありません。恐らくZiptronix社はソニーとライセンス契約を結んだことを公にして、自社パテントの優秀さを世に宣伝することが目的の発表だと思われます)

今回、上記パテントによって実現出来るであろう具体的な構造が示されたプレゼン資料が掲載されていましたので、採り上げたいと思います。

↑Ziptronix社が公表する(思う?)積層型センサ(Stacked Image Sensor)の歴史要点

しばらく前、上記サイトで、ソニーがZiptronixという聞きなれない会社から、新たに積層型センサのためのウェハ貼り合わせの特許ライセンス契約を結んだという様な内容のニュースを読んでいました。

(あくまで、上記情報をオープンにしたのはZiptronix社であって、ソニーがわざわざオープンにしている情報ではありません。恐らくZiptronix社はソニーとライセンス契約を結んだことを公にして、自社パテントの優秀さを世に宣伝することが目的の発表だと思われます)

今回、上記パテントによって実現出来るであろう具体的な構造が示されたプレゼン資料が掲載されていましたので、採り上げたいと思います。

↑Ziptronix社が公表する(思う?)積層型センサ(Stacked Image Sensor)の歴史要点

私、詳細は知らないのですが、このページの資料を見ると、(特にこの会社のパテントでは無いと思うのですが、)積層型センサの歴史は意外と古く、バンプ(半田ボールの様なもの?)でウェハを積層するアイデア自体は1977年からあるという様なことの様ですね。

で、一番右の”2012-”となっているところの図は、明らかにソニーのこのセンサのもので、そしてこれが初の”民生向け(≒Consumer)積層型BSI”ということの様です。

そして、このページで個人的に注目すべきは一番右下の(この後の話の前フリ部分に相当しているはずの)”No”per pixel”connections”の文字です。

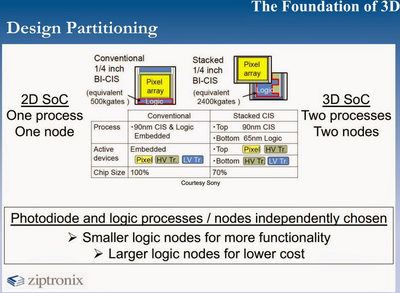

↑2~3ページ目の資料の主張は、上記2年前のソニーのISSCCでの”積層型センサのメリット”の主張をトレースするものですね。

具体的には、積層型センサにすれば・・・

・フォトダイオードとロジックプロセス世代を好き放題(≒独立して)選べる

例えば、以下の様な選択が可能

ロジックプロセスを微細にしてより機能を詰め込んだセンサ

ロジックプロセスに緩いルールのもの(≒多少古い世代のもの)を採用してコストダウン

・フォトダイオード基板とロジック基板(ウェハ)の供給ベンダーを別にすることも出来る

例えば、

ファブレス企業であれば、積層型のtopとbottom基板ウェハの供給元を別々に今までよりも多くの企業から競わせて選ぶことが可能になった (≒積層型センサでなければ、少なくともフォトダイオード≒イメージセンサを製造可能なFabからの選択肢しかあり得なかった)

IDM(垂直統合型企業)であれば、自社の競争力のあるコアな箇所(例えばフォトダイオードのtop基板側)に集中して、それ以外の(例えばbottom基板のロジック)部分は、よりコスト競争力のある外部Fabに委託するという選択肢も持てる様になる

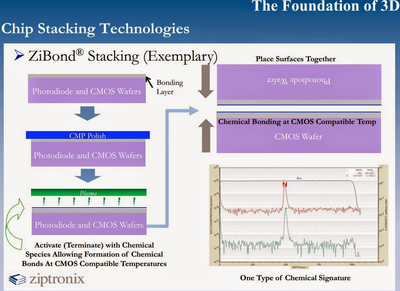

↑ 今までの積層型センサに使っていた技術(左:ZiBond・・・とこの会社では呼んでいるもののの様)と右:今回アピールしようとしているらしい”Hybrid DBI”という方式を、まず言葉で違いを説明したと思われるページ

【ZiBond】(左)

>単一の絶縁層で接着(?bond)

>基板接着後に三次元(≒垂直方向)内部接続

>TSV(Through Silicon Via)が必要

>コストが掛かる

>画素ごとの接続は無い

【Hybrid DBI】(右) ←DBI:どうもDirect Bond Interconnects の略のよう

>絶縁層とmetal層両方接着可能

>基板接着と同時に三次元内部接続可能

>TSV不要

>コストの最小化

>画素ごとのbottom基板との接続も可能

↑”ZiBond”なるものの方の製法説明の図のようです

つまるところ、現状のソニーの(そしてSamsungやその他の会社でも恐らく似た様なものではないかと思われる)積層型センサの製法の一部である”ウェハ貼りあわせ”の方法ですね。

私は理解している訳では無いですが、上図から、乱暴に言えば、

貼りあわせるお互いのウェハ表面に、貼りあわせ面となる絶縁層を堆積し、それをCMPで研磨し平坦化。その後、その表面をプラズマ処理して、CMOSプロセスで許容される温度(400℃以内くらい?)で熱処理しながら貼りあわせる、と。

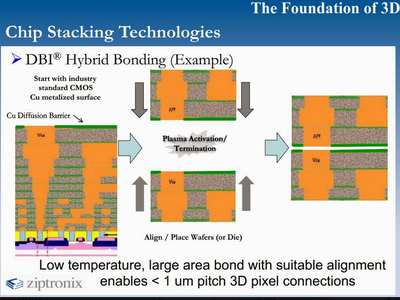

↑ そしてこちらが今回アピールしている”DBI Hybrid Bonding”の例の様です。

ZiBond製法が、一つ上の図面で”貼り合わせた後に”、TSVでフォトダイオードのあるtop側基板側から穴を開けて導通させるのに対し、このDirect Bonding Interconnects の方は、

張り合わせるお互いのウェハ表面に、”電気的に導通を図りたいViaを既に用意しておき”、図面で言うところのCu Diffusion Barrier 層とViaとなっているCuの双方のレイヤをプラズマで活性化させて貼りあわせる(≒貼りあわせることが可能)ということの様です。

この製法にすれば、この資料によれば、より低温で、より広範な領域を適切なアライメント精度で貼りあわせが可能ということのようで、

具体的には画素毎の接続も可能な1um以下のピッチでの導通も可能という風にアピールしています。

↑ 実際のDBI Hybrid Bonding の方で実際作られたウェハ貼りあわせ及びViaの接続部の断面の様です。

これを見ると、左上の25umピッチでのVia接続から、下の段は、左下が1.9umピッチ、右下が1.6umピッチで接続されています。

(前のページでZiptronixがアピールする"1um未満"というピッチでの実績はまだ無い様ではありますが、このアライメント精度が安定してウェハのどの領域においても実現できており、かつきちんと低抵抗で接続出来ているのであれば、)確かに”画素ごとに”一箇所までのViaの導通を前提とした回路及びデバイス設計のイメージセンサが実現出来そうです。

上図を見て、まず思い出すのが、昨年のNHKの技研公開時の三次元構造化技術のこの写真の技術。

接合したい電極界面をプラズマで活性化するあたりはそっくりですが、

このNHKの場合は、接合したい電極上に一度金(Au)を堆積しなければならないのに対して、本blogのZiptronixの特許の製法はCu Viaをそのまま接合出来そうです。

ですので、後発技術ながら(?)わかっている情報だけで判断するならこのZiptronixの技術の方が、現状CMOSプロセスとの親和性が高く、スジが良さそうな技術に感じます。

次に思い出すのが、二年前のISSCCでオリンパスが発表した画素ごとにbottom基板と電気的に接続したグローバルシャッタセンサです。

ただし、上記センサは正確には”4画素に一箇所”でしかbottom基板と接続出来ていません。

グローバルシャッタを実現したかった目的からすれば、本来1画素ごとにbottom基板と導通させたかったはずです。

この時、4画素に一つの導通にせざるを得なかったのは、恐らくその導通手段がマイクロバンプと呼んでいる接続方法であったため、最小ピッチが1画素では、どうしても製造することが出来なかったからだと思われます。

ですので、オリンパスが上記ISSCC発表のグローバルシャッタセンサの商品化に、もし本気なのであれば、

ソニーがこのZiptronixパテントを元にした画素毎にbottom基板とtop基板を導通させる技術を確立後に、ソニー経由で使用Fabに製造を委託すれば、オリンパスが当初行いたかったと思われるbottom基板側に画素毎に必要な容量等を保持したグローバルシャッタセンサが製造できそうです。

(↑あくまで生産数量とコスト面で両者が折り合えれば・・・の話ですが^^;)

その次に思い出すのが、OmniVisionと恐らくTSMCのこの積層プラン。

恐らくOmniVisionはまだ積層型センサ製品を量産出荷したことは無さそうで、現在サンプル出荷中の状態のコレがOmniの初積層型センサの様子。今年下半期から量産出荷予定の様です。

で、恐らく最初の量産品なのでこの図の一番左の積層タイプから始めるのではないかと個人的には予想します。

その場合には、現在のソニーの様に画素周辺の列及び行回路のどこかでTSVを用いてtopとbottom基板の導通を取ってつなぐことになりそうです。

その次にOmniが手がける予定(?)なのがこの図の中央の積層タイプで、このタイプは図と説明を見る限りは全く今回blogエントリしたZiptronixの特許の件と(製法は異なる可能性はありますが)やろうとしていることは全く同じに思えます。

各社、向かう先はやはり一緒(似ている)ですかね(^^;)

今後、ソニーはこの技術の量産性が無事確保されたあかつきには、

1) 微細画素センサ ←今後、どこまで画素ピッチを狭くするのかわかりませんが

2) 画素に何かの機能を積み込みたいセンサ

上記の様なセンサに関しては、このZiptronixの供与パテントの構造を採用するのではないでしょうか。

当たり前かもしれませんが、全てのセンサでは無いと思います。

というのも、つい最近もエントリした、ソニーのISSCCの列ADCもbottom基板側に配置させて、チップの投影面積を極力抑える設計方針と、このZiptronixの製法を使ったチップは相反するように思うからです。

このZiptronix製法(?)の構造にすると、当然画素領域直下のbottom基板は全てその画素の何がしかの素子で埋まってしまいます。

ですので、信号の読み出し&処理回路を画素領域直下に配置するスペースはなくなってしまい、素直に考えればbottom基板側の画素領域外に必要なオンチップの周辺処理回路を配置しなくてはなりません。これだと今までの積層型(stacked型)ではないFSIやBSIセンサと同様のチップ面積に戻ってしまいます。

ですので、上記の通り、この画素毎にbottom基板に導通が取れると大きなメリットが得られるセンサにしか適用はしないだろうと思う訳ですが、

唯一(?)技術的に、上記トレードオフを逃れられる術と感じるのが、この一番右の”3ウェハstacking”となっている構造です。

名称の通り、3ウェハを重ねていて、画素毎の導通をmiddle基板と取り、更には周辺部において、top-middle-bottom基板の電気的導通をTSVで取るという方法です。

この方法であれば、画素毎にmiddle基板に追加機能のための(?)トランジスタなどの素子を置きつつも、一番下のbottom基板に今まで通り、信号処理などのための回路を配置することが可能です。

結果、現在のソニーセンサの様に、撮像領域+αの投影面積のチップサイズで、画素毎にmiddle基板に導通を取ったセンサが実現可能です。

ただ・・・上記の様な3ウェハスタッキング構造にすると、基板代や当然流動の工程数増加、歩留まりの低下等により、コストは跳ね上がると予想されます。

そこまでのデメリットを押してもお釣りがくる様な画期的な機能や用途を見つけ出したイメージセンサにしか、3ウェハstacking構造は採用できないのでは?と思うのですが、

技術の進歩は早くて、それ以上に大した追加コスト無く、この構造が実現できるようになったりするのでしょうか?

長くなりましたが、今回言いたいことは以上なのですが、余談であともう一点。

もし、ソニーなどがこのZiptronixパテントの構造を持つ撮像素子を実現し、何がしかの用途でこの構造のセンサが従来センサに対して圧倒的なコストパフォーマンスを発揮した場合、

現在、FSI(表面照射型)センサ”しか”製造出来ない企業は、その”何がしか”の用途向けセンサの市場からの退出を余儀なくされることになると思います。

というのも、私が偉そうに書くことでもありませんが、このZiptronixパテントの構造は、明らかにFSIセンサとの親和性が悪い=FSIセンサでは事実上実現しても効果が薄い?からです。

裏面照射型センサは、自然とウェハ貼り合わせ面側に、画素の電気配線がむき出しになる(?)ことになりますが、表面照射型センサは貼り合せ面と画素メタル配線の間にフォトダイオードがある構造になってしまいます。

すると、フォトダイオードの面積を削ってまで、TSV等の技術でbottom基板と導通を取る必要が出てきますが、

それをやってしまうと、相当の大画素ピッチセンサしか特性上機能上のメリットがなくなってしまいそうです。

また逆説的には、そんな画素ごとTSV技術を持っているような企業なら裏面照射型センサ製造の技術も持っていそうなので、素直に裏面照射型センサで画素毎導通を取る構造を選択すると思います。

ですので、FSIしか作れない企業は上記”何がしかの用途”向けセンサ市場からの退出を余儀なくされるかなと思った次第です。

で、一番右の”2012-”となっているところの図は、明らかにソニーのこのセンサのもので、そしてこれが初の”民生向け(≒Consumer)積層型BSI”ということの様です。

そして、このページで個人的に注目すべきは一番右下の(この後の話の前フリ部分に相当しているはずの)”No”per pixel”connections”の文字です。

↑2~3ページ目の資料の主張は、上記2年前のソニーのISSCCでの”積層型センサのメリット”の主張をトレースするものですね。

具体的には、積層型センサにすれば・・・

・フォトダイオードとロジックプロセス世代を好き放題(≒独立して)選べる

例えば、以下の様な選択が可能

ロジックプロセスを微細にしてより機能を詰め込んだセンサ

ロジックプロセスに緩いルールのもの(≒多少古い世代のもの)を採用してコストダウン

・フォトダイオード基板とロジック基板(ウェハ)の供給ベンダーを別にすることも出来る

例えば、

ファブレス企業であれば、積層型のtopとbottom基板ウェハの供給元を別々に今までよりも多くの企業から競わせて選ぶことが可能になった (≒積層型センサでなければ、少なくともフォトダイオード≒イメージセンサを製造可能なFabからの選択肢しかあり得なかった)

IDM(垂直統合型企業)であれば、自社の競争力のあるコアな箇所(例えばフォトダイオードのtop基板側)に集中して、それ以外の(例えばbottom基板のロジック)部分は、よりコスト競争力のある外部Fabに委託するという選択肢も持てる様になる

↑ 今までの積層型センサに使っていた技術(左:ZiBond・・・とこの会社では呼んでいるもののの様)と右:今回アピールしようとしているらしい”Hybrid DBI”という方式を、まず言葉で違いを説明したと思われるページ

【ZiBond】(左)

>単一の絶縁層で接着(?bond)

>基板接着後に三次元(≒垂直方向)内部接続

>TSV(Through Silicon Via)が必要

>コストが掛かる

>画素ごとの接続は無い

【Hybrid DBI】(右) ←DBI:どうもDirect Bond Interconnects の略のよう

>絶縁層とmetal層両方接着可能

>基板接着と同時に三次元内部接続可能

>TSV不要

>コストの最小化

>画素ごとのbottom基板との接続も可能

↑”ZiBond”なるものの方の製法説明の図のようです

つまるところ、現状のソニーの(そしてSamsungやその他の会社でも恐らく似た様なものではないかと思われる)積層型センサの製法の一部である”ウェハ貼りあわせ”の方法ですね。

私は理解している訳では無いですが、上図から、乱暴に言えば、

貼りあわせるお互いのウェハ表面に、貼りあわせ面となる絶縁層を堆積し、それをCMPで研磨し平坦化。その後、その表面をプラズマ処理して、CMOSプロセスで許容される温度(400℃以内くらい?)で熱処理しながら貼りあわせる、と。

↑ そしてこちらが今回アピールしている”DBI Hybrid Bonding”の例の様です。

ZiBond製法が、一つ上の図面で”貼り合わせた後に”、TSVでフォトダイオードのあるtop側基板側から穴を開けて導通させるのに対し、このDirect Bonding Interconnects の方は、

張り合わせるお互いのウェハ表面に、”電気的に導通を図りたいViaを既に用意しておき”、図面で言うところのCu Diffusion Barrier 層とViaとなっているCuの双方のレイヤをプラズマで活性化させて貼りあわせる(≒貼りあわせることが可能)ということの様です。

この製法にすれば、この資料によれば、より低温で、より広範な領域を適切なアライメント精度で貼りあわせが可能ということのようで、

具体的には画素毎の接続も可能な1um以下のピッチでの導通も可能という風にアピールしています。

↑ 実際のDBI Hybrid Bonding の方で実際作られたウェハ貼りあわせ及びViaの接続部の断面の様です。

これを見ると、左上の25umピッチでのVia接続から、下の段は、左下が1.9umピッチ、右下が1.6umピッチで接続されています。

(前のページでZiptronixがアピールする"1um未満"というピッチでの実績はまだ無い様ではありますが、このアライメント精度が安定してウェハのどの領域においても実現できており、かつきちんと低抵抗で接続出来ているのであれば、)確かに”画素ごとに”一箇所までのViaの導通を前提とした回路及びデバイス設計のイメージセンサが実現出来そうです。

上図を見て、まず思い出すのが、昨年のNHKの技研公開時の三次元構造化技術のこの写真の技術。

接合したい電極界面をプラズマで活性化するあたりはそっくりですが、

このNHKの場合は、接合したい電極上に一度金(Au)を堆積しなければならないのに対して、本blogのZiptronixの特許の製法はCu Viaをそのまま接合出来そうです。

ですので、後発技術ながら(?)わかっている情報だけで判断するならこのZiptronixの技術の方が、現状CMOSプロセスとの親和性が高く、スジが良さそうな技術に感じます。

次に思い出すのが、二年前のISSCCでオリンパスが発表した画素ごとにbottom基板と電気的に接続したグローバルシャッタセンサです。

ただし、上記センサは正確には”4画素に一箇所”でしかbottom基板と接続出来ていません。

グローバルシャッタを実現したかった目的からすれば、本来1画素ごとにbottom基板と導通させたかったはずです。

この時、4画素に一つの導通にせざるを得なかったのは、恐らくその導通手段がマイクロバンプと呼んでいる接続方法であったため、最小ピッチが1画素では、どうしても製造することが出来なかったからだと思われます。

ですので、オリンパスが上記ISSCC発表のグローバルシャッタセンサの商品化に、もし本気なのであれば、

ソニーがこのZiptronixパテントを元にした画素毎にbottom基板とtop基板を導通させる技術を確立後に、ソニー経由で使用Fabに製造を委託すれば、オリンパスが当初行いたかったと思われるbottom基板側に画素毎に必要な容量等を保持したグローバルシャッタセンサが製造できそうです。

(↑あくまで生産数量とコスト面で両者が折り合えれば・・・の話ですが^^;)

その次に思い出すのが、OmniVisionと恐らくTSMCのこの積層プラン。

恐らくOmniVisionはまだ積層型センサ製品を量産出荷したことは無さそうで、現在サンプル出荷中の状態のコレがOmniの初積層型センサの様子。今年下半期から量産出荷予定の様です。

で、恐らく最初の量産品なのでこの図の一番左の積層タイプから始めるのではないかと個人的には予想します。

その場合には、現在のソニーの様に画素周辺の列及び行回路のどこかでTSVを用いてtopとbottom基板の導通を取ってつなぐことになりそうです。

その次にOmniが手がける予定(?)なのがこの図の中央の積層タイプで、このタイプは図と説明を見る限りは全く今回blogエントリしたZiptronixの特許の件と(製法は異なる可能性はありますが)やろうとしていることは全く同じに思えます。

各社、向かう先はやはり一緒(似ている)ですかね(^^;)

今後、ソニーはこの技術の量産性が無事確保されたあかつきには、

1) 微細画素センサ ←今後、どこまで画素ピッチを狭くするのかわかりませんが

2) 画素に何かの機能を積み込みたいセンサ

上記の様なセンサに関しては、このZiptronixの供与パテントの構造を採用するのではないでしょうか。

当たり前かもしれませんが、全てのセンサでは無いと思います。

というのも、つい最近もエントリした、ソニーのISSCCの列ADCもbottom基板側に配置させて、チップの投影面積を極力抑える設計方針と、このZiptronixの製法を使ったチップは相反するように思うからです。

このZiptronix製法(?)の構造にすると、当然画素領域直下のbottom基板は全てその画素の何がしかの素子で埋まってしまいます。

ですので、信号の読み出し&処理回路を画素領域直下に配置するスペースはなくなってしまい、素直に考えればbottom基板側の画素領域外に必要なオンチップの周辺処理回路を配置しなくてはなりません。これだと今までの積層型(stacked型)ではないFSIやBSIセンサと同様のチップ面積に戻ってしまいます。

ですので、上記の通り、この画素毎にbottom基板に導通が取れると大きなメリットが得られるセンサにしか適用はしないだろうと思う訳ですが、

唯一(?)技術的に、上記トレードオフを逃れられる術と感じるのが、この一番右の”3ウェハstacking”となっている構造です。

名称の通り、3ウェハを重ねていて、画素毎の導通をmiddle基板と取り、更には周辺部において、top-middle-bottom基板の電気的導通をTSVで取るという方法です。

この方法であれば、画素毎にmiddle基板に追加機能のための(?)トランジスタなどの素子を置きつつも、一番下のbottom基板に今まで通り、信号処理などのための回路を配置することが可能です。

結果、現在のソニーセンサの様に、撮像領域+αの投影面積のチップサイズで、画素毎にmiddle基板に導通を取ったセンサが実現可能です。

ただ・・・上記の様な3ウェハスタッキング構造にすると、基板代や当然流動の工程数増加、歩留まりの低下等により、コストは跳ね上がると予想されます。

そこまでのデメリットを押してもお釣りがくる様な画期的な機能や用途を見つけ出したイメージセンサにしか、3ウェハstacking構造は採用できないのでは?と思うのですが、

技術の進歩は早くて、それ以上に大した追加コスト無く、この構造が実現できるようになったりするのでしょうか?

長くなりましたが、今回言いたいことは以上なのですが、余談であともう一点。

もし、ソニーなどがこのZiptronixパテントの構造を持つ撮像素子を実現し、何がしかの用途でこの構造のセンサが従来センサに対して圧倒的なコストパフォーマンスを発揮した場合、

現在、FSI(表面照射型)センサ”しか”製造出来ない企業は、その”何がしか”の用途向けセンサの市場からの退出を余儀なくされることになると思います。

というのも、私が偉そうに書くことでもありませんが、このZiptronixパテントの構造は、明らかにFSIセンサとの親和性が悪い=FSIセンサでは事実上実現しても効果が薄い?からです。

裏面照射型センサは、自然とウェハ貼り合わせ面側に、画素の電気配線がむき出しになる(?)ことになりますが、表面照射型センサは貼り合せ面と画素メタル配線の間にフォトダイオードがある構造になってしまいます。

すると、フォトダイオードの面積を削ってまで、TSV等の技術でbottom基板と導通を取る必要が出てきますが、

それをやってしまうと、相当の大画素ピッチセンサしか特性上機能上のメリットがなくなってしまいそうです。

また逆説的には、そんな画素ごとTSV技術を持っているような企業なら裏面照射型センサ製造の技術も持っていそうなので、素直に裏面照射型センサで画素毎導通を取る構造を選択すると思います。

ですので、FSIしか作れない企業は上記”何がしかの用途”向けセンサ市場からの退出を余儀なくされるかなと思った次第です。

PR

コメント

ブログ内検索

カウンター

最新コメント

[03/28 hoge]

[03/26 hi-low]

[03/22 山川]

[03/18 hoge]

[03/08 hi-low]

[03/04 hoge]

[02/26 山川]

[02/26 山川]

[02/19 hoge]

[02/18 山川]

[02/05 hoge]

[02/05 hi-low]

[01/29 通りすがりです]

[01/28 FT]

[01/23 hi-low]

カテゴリー

カレンダー

最新記事

(04/22)

(04/01)

(03/25)

(03/17)

(03/11)

最古記事

プロフィール

HN:

imagerマニア

性別:

非公開