Imager マニア

デジカメ / デジタルビデオカメラ / スマホ用の撮像素子(イメージセンサ/imager/CMOSセンサ)について、マニアな情報や私見を徒然なるままに述べるBlogです(^^;)

[PR]

×

[PR]上記の広告は3ヶ月以上新規記事投稿のないブログに表示されています。新しい記事を書く事で広告が消えます。

ニコンのミラーレスカメラの高速連写性能の謎 ~Aptina製1インチCMOSセンサの高速読み出し技術

前回のblogでCMOSIS製のグローバルシャッタ搭載センサを取り挙げたのですが、コメント欄でのやりとりで、ふと・・・

”グローバルシャッタ搭載のメリットはローリングシャッタ歪みとフラッシュバンド現象の回避だけれども、高速に読み出せるCMOSセンサであれば(グローバルシャッタ機能は無くとも)上記問題の完全解決は無理にしても、(私の様な記念or記録写真しか撮らない一般人にとって)実用的で問題の無いものになるんだよな”

と思う様になりました(←またその内考えが変わるかもしれませんが(^^;))。

で、”現状市販されているカメラで他を圧倒して高速連写が可能なカメラがあるな”と。

(※本質的には”高速連写出来る”ということとローリングシャッタ歪みの出る/出ないに1:1の因果関係は無いはずですが、高速連写可能≒センサの読み出しスピードが速くなければ不可能⇒CMOSセンサを画面の上から下まで読み出すのに必要な時間が少ないので比較的ローリングシャッタ歪みが出難いという間接的な因果関係はあると思います。←逆は必ずしも成立せず、センサの読み出しスピードが速くても、カメラ製品側の何等かの理由によりカメラスペックとしての連写スピードは抑えられている可能性があるため、連写スピードが遅いカメラの方が必ずローリングシャッタ歪みが大きいと決まる訳ではないはず)

それがニコンのミラーレス群。

脅威の60コマ/Sec。私に言わせれば最早これは静止画ではなく動画の域です(^^;)

※上記は動画モードの話ではなく、静止画撮影のフル解像度読み出しでのspecです。

比較のための、高速連写が売りの他のカメラの数字を記載すると・・・

キヤノン1Dx:14コマ/Sec (ピント・露出は連写一枚目固定の高速連写モード時)

ニコンD4 :11コマ/Sec (ピント・露出は保証されない高速連写モード時)

ソニーα77V :12コマ/Sec (露出保証外の高速連写モード)

カシオ ハイスピードエクシリム全般 :30コマ/Sec

※上の三つのカメラはフォーカルプレーンシャッターが存在するため、少なくとも静止画撮影時のローリングシャッタ歪みはこの連写速度とは無関係になると思われます。単に連写の比較として参考に。

(画素数が同じでは無いので、単純比較はよくないですが)カシオのコンパクトもかなりのものですが、やはりニコンミラーレス群が頭二つほど抜けているのがわかります。

そしてそんなニコンのミラーレスカメラに搭載されているセンサの製造メーカーはAptinaということも既にchipworks等の解析でわかっています。(←少なくとも初代のニコン1 V1は間違い無く、その後も変わっていないものと予想されます。←カメラのスペックとAptinaが発表するセンサスペックとを比較すると)

↑ 2013年 IISW時 Aptina(アプティナ)からの報告資料写真から

と、言う訳で、今回のエントリは、上記Aptina(アプティナ)社の報告資料から、Aptina製センサが高速読み出し可能な理由の一端を見ていきたいと思います。

”グローバルシャッタ搭載のメリットはローリングシャッタ歪みとフラッシュバンド現象の回避だけれども、高速に読み出せるCMOSセンサであれば(グローバルシャッタ機能は無くとも)上記問題の完全解決は無理にしても、(私の様な記念or記録写真しか撮らない一般人にとって)実用的で問題の無いものになるんだよな”

と思う様になりました(←またその内考えが変わるかもしれませんが(^^;))。

で、”現状市販されているカメラで他を圧倒して高速連写が可能なカメラがあるな”と。

(※本質的には”高速連写出来る”ということとローリングシャッタ歪みの出る/出ないに1:1の因果関係は無いはずですが、高速連写可能≒センサの読み出しスピードが速くなければ不可能⇒CMOSセンサを画面の上から下まで読み出すのに必要な時間が少ないので比較的ローリングシャッタ歪みが出難いという間接的な因果関係はあると思います。←逆は必ずしも成立せず、センサの読み出しスピードが速くても、カメラ製品側の何等かの理由によりカメラスペックとしての連写スピードは抑えられている可能性があるため、連写スピードが遅いカメラの方が必ずローリングシャッタ歪みが大きいと決まる訳ではないはず)

それがニコンのミラーレス群。

脅威の60コマ/Sec。私に言わせれば最早これは静止画ではなく動画の域です(^^;)

※上記は動画モードの話ではなく、静止画撮影のフル解像度読み出しでのspecです。

比較のための、高速連写が売りの他のカメラの数字を記載すると・・・

キヤノン1Dx:14コマ/Sec (ピント・露出は連写一枚目固定の高速連写モード時)

ニコンD4 :11コマ/Sec (ピント・露出は保証されない高速連写モード時)

ソニーα77V :12コマ/Sec (露出保証外の高速連写モード)

カシオ ハイスピードエクシリム全般 :30コマ/Sec

※上の三つのカメラはフォーカルプレーンシャッターが存在するため、少なくとも静止画撮影時のローリングシャッタ歪みはこの連写速度とは無関係になると思われます。単に連写の比較として参考に。

(画素数が同じでは無いので、単純比較はよくないですが)カシオのコンパクトもかなりのものですが、やはりニコンミラーレス群が頭二つほど抜けているのがわかります。

そしてそんなニコンのミラーレスカメラに搭載されているセンサの製造メーカーはAptinaということも既にchipworks等の解析でわかっています。(←少なくとも初代のニコン1 V1は間違い無く、その後も変わっていないものと予想されます。←カメラのスペックとAptinaが発表するセンサスペックとを比較すると)

↑ 2013年 IISW時 Aptina(アプティナ)からの報告資料写真から

と、言う訳で、今回のエントリは、上記Aptina(アプティナ)社の報告資料から、Aptina製センサが高速読み出し可能な理由の一端を見ていきたいと思います。

まず、この報告資料のセンサですが、恐らくAptina社のHPに記載されているこのセンサと同じと思います(←特性面で若干異なるところが見受けられますが、違うセンサだったとしても微修正で大枠の技術はこの報告資料の内容と同一と見て良いと思います)。

そして、このセンサはニコンのミラーレスカメラJ1~J2、そして現行機種のs1まで使われているものと予想されます。

今回、私がこのAptinaの発表資料を見て興味を惹かれた点は以下です。

①フレームレート(≒信号読み出し速度)の目標値を、ローリングシャッター歪みを気にして決定していること

②オンチップADの方式が逐次比較方であったこと

※読み出しスピードが速いことと直接関係があるかはこの資料だけでは不明

③1行の読み出し時間が具体的に記されている

④"Nesting scan"と彼らが呼んでいる、イレギュラーな行読み出し順序 (を行うことによって高速化を果たしていること)

①に関しては、この発表資料の冒頭部分で語られています。

大まかにこの発表資料の導入部分の話の流れを私の解釈で意訳すると・・・

1)我々は未来のカメラはメカニカルシャッターが無くなると信じている

2)何故ならば、既に(ミラーレスカメラは一眼レフカメラに対して)ミラーとプリズムがなくなっており、これに加えてメカニカルシャッタが無くなれば、

より小型、軽量、信頼性の向上が見込まれるからだ

↑実際にスペック表を見ると、ニコンのミラーレスのJとSのシリーズはメカニカルシャッターレスとなっています。

3)しかし、CMOS imagerの宿命として、メカニカルシャッタを無くすと、動体のローリングシャッタ歪みが問題となる。

4)ローリングシャッター歪みを無くすためには、グローバルシャッタ搭載か、センサの読み出しスピードを速くするかのどちらかが必要だ

5)しかし、静止画で考えた際のトータルパフォーマンスは、グローバルシャッタ方式よりもローリングシャッタ方式の方にアドバンテージがある

↑どの辺にアドバンテージがあるのか、ここでは触れられていませんでした。

6)そこで我々はローリングシャッター方式で80fpsという読み出しスピードを選ぶ(目標とする)ことにした

7)80fpsというスピードを選んだ理由は・・・

1970~80年代のカメラのメカニカルシャッターのスピードがそのくらいであった

というのと、

通常の写真useで求められる最低限のレベル

であると判断したからだ

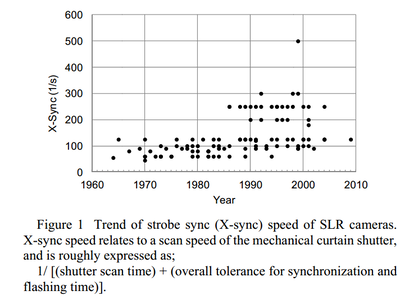

↑ 発表資料内でAptinaが1970~80年代のメカニカルシャッタのスキャンスピードを1/80Sec程度であるとの根拠としたグラフ

概略の理解としてはストロボ(フラッシュ)の同調速度の最短のシャッタースピードを縦軸にプロットしたようなものだと思われます。

この冒頭の話の流れは、このblogエントリをしようと思った私の動機とあまりにぴったり一致していてビックリしました。

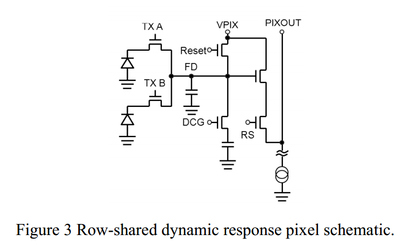

↑画素の等価回路図

縦方向の2画素でFDとSFアンプを共有するもの。←よくある画素のレイアウト効率up(開口率up)のためだと思われます。

今回③のNesting scanと少し関係があるので。

また、余談ですが、今回の件の本題では無いはずですが、例の以前本blogで取り挙げた”Dual Conversion Gain”(←上記回路図のDCGのスイッチとその下の容量の使い方)についても、本発表資料では触れられています。

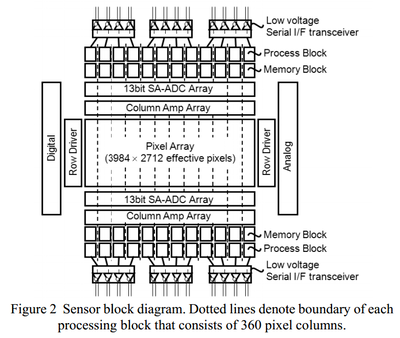

↑発表資料内のセンサブロックダイヤグラム

②のオンチップのADCが逐次比較型であった件ですが、

Aptinaとしては、今回の発表したい内容ではなかったので、本文内でほとんど触れていませんが、本文と上記図面の”13bit SA-ADC Array”の記述から、Aptina社の(少なくともニコンミラーレスに採用されている)センサのAD方式はSA(successive approximation)方式=逐次比較型の列ADであることがわかりました。

少なくとも私は今回初めて上記を知りました。

この件については、もし他の文献や特許を見つけることが出来たら、個人的には興味があるのでもう少し追ってみようかなと思います。

それと余談ですが、上記ブロック図と本文の記載から、信号出力はセンサの上下端から、水平方向に12分割されたブロックを更に上下に2分割した計24チャンネル(?)で出力されることがわかります。

これ、センサ外で信号処理するニコン側が結構面倒そうだなと思いました。

これに関して多くのセンサの情報を集めた訳ではありませんが、普通は1行の中で左からなら左から、右からなら右から順次センサ信号が出力されると思われるからです。

このアプティナの出力方法だと、ブロック毎に端からデータが出てくるので、センサ外で信号順序をどこかで入れ替えなければならなくなるだろうからです。

しかし、これもこのセンサの高速読み出しに一役買っているかもしれませんね。

高速信号をセンサの水平方向の端から端まで読み出すのは(スピード、もしくは電力的に)面倒な話ですから、この様に水平方向にある程度のブロックに分割して、最も近い出力端子から読み出してしまうというは、センサ単体で見ればスピード的もしくは電力的に効率の良い方法だと感じました。

↑ 本発表資料より pixel-to-ADC pipelined operetion説明図

私の興味ありリストに入れていませんが、本発表資料の格子の一つ

画素信号読み出し / AD変換&CDS / メモリからの信号読み出し の3つをパイプライン読み出し(=並列読み出し)している

という説明図。

まず、「今回の高速化の基本はこれですよ」という意図の説明だと思います。

ただ、予想で恐縮ですが、多かれ少なかれAptina以外の会社のセンサも同様のパイプライン処理は行っているのではと思います。

よって今回上図の詳細説明は割愛。

そしてここで③の”1行の読み出し時間が具体的に記されている”です。

上記パイプライン処理を考慮した、1行の読み出しに要する時間は、4.58uSecということです。

上図センサブロックダイヤグラム内で、有効画素数の行数が2712。

ざっくり1フレーム読み出すのに必要な時間は、4.58μSec×2712行≒0.0124Sec

1Sec/0.0124Sec≒80fps

ということで、当たり前ですがこのセンサのフレームレートと辻褄は合いそうです。

加えて本文中の文章でフォローすると

・このパイプライン処理によって、リセット及び信号レベルのサンプリングにそれぞれ1.6uSec(上図の”OS”及び”SIG”の期間にそれぞれ該当すると思われる)の時間を取ることが出来た

しかし、ここで”あれ?”となります。

上図では、1行目の信号を読み出したりしている最中に2行目のFDがリセットされている図になっています。

”これじゃ1行目の信号まともに読み出せないよ!(笑)”

何故なら1行目と2行目のFDは共通なのですから、どちらかの信号を読みたければ、FDはリセット出来ないからです。

と、内心小馬鹿にしていたら、間違いでは無く予想に反する回答(?)が載っていました。

↑発表資料より Nesting scanの読み出し方

※基本的に左の図をみるのがわかりやすいと思います。

その回答が④Nesting scan です。

画素のFDを縦方向の2画素で共有していることが前提です。←逆に言うと2画素で共有していなければこんな工夫は不要です。

3.4um□の微細な画素ピッチであるから必要な工夫と言い換えることも可能かもしれません。

つまり、上から順に行信号を読まずに、左上図の様に

#0(行目) ⇒ #2 ⇒ #1 ⇒ #3 ⇒ #4 ⇒ #6 ⇒ #5 ⇒ ・・・

という様に、FDを共有している画素行を続けて読むことが無いような走査順になっているのです!

(さきほどの水平方向でブロック毎に信号が読みだされてくることと合わせて)これまた何と後段でのデータ処理泣かせな(^^;)

ニコンという会社はどんな信号出力順でも、「後ろで並べ替えOKよ」という受けの広さを持っている様です。

これによるメリットは以下の様に具体的数字を持って示されています。

・従来のFDリセットの方法では、FDをリセットするのに(パルスのセトリングとそのばらつきも含めて)0.8~1uSecの時間を要した

⇒そんため、今回の(次に読む行は既にFDリセットされた状態からスタート出来る)Nesting scan方式では、リセット及び信号レベルのサンプリングにそれぞれ0.5uSecずつ時間を余計に割り振ることが可能になった

・同時に、もし仮に従来の方式のままであれば(0.5uSecずつ短い時間でリセットと信号レベルのサンプリングを行う必要があるため)約1.5倍の画素定電流と列アンプ定電流をそれぞれ流す必要があった。

⇒そのため、今回のNesting scan方式を取ることによって、同時に(同じ読み出しスピードを達成するのであれば)低消費電力化も図られている

今回、このNesting scanという(呼び方の名前の由来は不明ですが)読み出し順序の工夫に、私は一番衝撃を受けました。

その他、分光(量子効率)や、Dual Conversion Gain それぞれの際のノイズ及びその他の諸特性が報告されていますが、そちらは本論ではなさそうなので割愛。

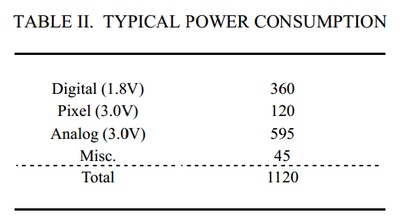

最後に、低消費電力化を図られた後の各部の消費電力と、トータルの消費電力の他社比較が載せられています。

トータル1120mW。

今回、Nesting scan方式によって、読み出しスピードを高速化した割には消費電力の増大を抑えられたはずのAnalog(3.0V)ですが、それでもこの分類では最も電力食いな状態になっています。

まあデジタルと電源電圧が異なるので仕方が無いのでしょうか。

↑他社センサ比較

ちなみにこの[4]~[7]というのは引用文献の符番(?)となっており、調べるとそれぞれ以下の会社のセンサになっていました

[4]:Micron (マイクロン) 1085mW

※Aptinaはマイクロンのイメージセンサ部門が分社して出来た会社ですので、これが事実上の自社の以前のセンサ比

[5]ソニー 975mW ADCは分解能10bitのシングルスロープ方式

[6]ソニー 3000mW

[7]静岡大学×NHK×ブルックマンズテクノロジー 2670mW ADCはサイクリック方式

※どうも一番右端列の”FoM”という値は、画素数とフレームレートと出力bit数と消費電力とノイズを絡ませた指数の様です。

単純には上記値が”小さい方が良いセンサだ”と言いたい様です。

本発表資料の最後は(私の意訳では)ざっくり以下の様に締めくくっています。

「ハイエンドカメラとビデオに許容される(≒相応しい)特性の1インチセンサが出来た。

(上図を示して)他社と比較して、最も良いバランスのセンサだろう?」

比較対象の中で最も古いセンサが2010年に発表されたもの。今回のaptina報告のセンサと最大で3年の差があるのと、何となく上記”FoM”という指標が、”自社のセンサが最も有利になる指標にはどういうものがあるか?”という観点から逆に探し出したような胡散臭さを覚える指標であること

という二点の怪しさは感じなくもないですが、読み出しスピードに関して凄いセンサであることは間違い無い様に思います。

そして、このセンサはニコンのミラーレスカメラJ1~J2、そして現行機種のs1まで使われているものと予想されます。

今回、私がこのAptinaの発表資料を見て興味を惹かれた点は以下です。

①フレームレート(≒信号読み出し速度)の目標値を、ローリングシャッター歪みを気にして決定していること

②オンチップADの方式が逐次比較方であったこと

※読み出しスピードが速いことと直接関係があるかはこの資料だけでは不明

③1行の読み出し時間が具体的に記されている

④"Nesting scan"と彼らが呼んでいる、イレギュラーな行読み出し順序 (を行うことによって高速化を果たしていること)

①に関しては、この発表資料の冒頭部分で語られています。

大まかにこの発表資料の導入部分の話の流れを私の解釈で意訳すると・・・

1)我々は未来のカメラはメカニカルシャッターが無くなると信じている

2)何故ならば、既に(ミラーレスカメラは一眼レフカメラに対して)ミラーとプリズムがなくなっており、これに加えてメカニカルシャッタが無くなれば、

より小型、軽量、信頼性の向上が見込まれるからだ

↑実際にスペック表を見ると、ニコンのミラーレスのJとSのシリーズはメカニカルシャッターレスとなっています。

3)しかし、CMOS imagerの宿命として、メカニカルシャッタを無くすと、動体のローリングシャッタ歪みが問題となる。

4)ローリングシャッター歪みを無くすためには、グローバルシャッタ搭載か、センサの読み出しスピードを速くするかのどちらかが必要だ

5)しかし、静止画で考えた際のトータルパフォーマンスは、グローバルシャッタ方式よりもローリングシャッタ方式の方にアドバンテージがある

↑どの辺にアドバンテージがあるのか、ここでは触れられていませんでした。

6)そこで我々はローリングシャッター方式で80fpsという読み出しスピードを選ぶ(目標とする)ことにした

7)80fpsというスピードを選んだ理由は・・・

1970~80年代のカメラのメカニカルシャッターのスピードがそのくらいであった

というのと、

通常の写真useで求められる最低限のレベル

であると判断したからだ

↑ 発表資料内でAptinaが1970~80年代のメカニカルシャッタのスキャンスピードを1/80Sec程度であるとの根拠としたグラフ

概略の理解としてはストロボ(フラッシュ)の同調速度の最短のシャッタースピードを縦軸にプロットしたようなものだと思われます。

この冒頭の話の流れは、このblogエントリをしようと思った私の動機とあまりにぴったり一致していてビックリしました。

↑画素の等価回路図

縦方向の2画素でFDとSFアンプを共有するもの。←よくある画素のレイアウト効率up(開口率up)のためだと思われます。

今回③のNesting scanと少し関係があるので。

また、余談ですが、今回の件の本題では無いはずですが、例の以前本blogで取り挙げた”Dual Conversion Gain”(←上記回路図のDCGのスイッチとその下の容量の使い方)についても、本発表資料では触れられています。

↑発表資料内のセンサブロックダイヤグラム

②のオンチップのADCが逐次比較型であった件ですが、

Aptinaとしては、今回の発表したい内容ではなかったので、本文内でほとんど触れていませんが、本文と上記図面の”13bit SA-ADC Array”の記述から、Aptina社の(少なくともニコンミラーレスに採用されている)センサのAD方式はSA(successive approximation)方式=逐次比較型の列ADであることがわかりました。

少なくとも私は今回初めて上記を知りました。

この件については、もし他の文献や特許を見つけることが出来たら、個人的には興味があるのでもう少し追ってみようかなと思います。

それと余談ですが、上記ブロック図と本文の記載から、信号出力はセンサの上下端から、水平方向に12分割されたブロックを更に上下に2分割した計24チャンネル(?)で出力されることがわかります。

これ、センサ外で信号処理するニコン側が結構面倒そうだなと思いました。

これに関して多くのセンサの情報を集めた訳ではありませんが、普通は1行の中で左からなら左から、右からなら右から順次センサ信号が出力されると思われるからです。

このアプティナの出力方法だと、ブロック毎に端からデータが出てくるので、センサ外で信号順序をどこかで入れ替えなければならなくなるだろうからです。

しかし、これもこのセンサの高速読み出しに一役買っているかもしれませんね。

高速信号をセンサの水平方向の端から端まで読み出すのは(スピード、もしくは電力的に)面倒な話ですから、この様に水平方向にある程度のブロックに分割して、最も近い出力端子から読み出してしまうというは、センサ単体で見ればスピード的もしくは電力的に効率の良い方法だと感じました。

↑ 本発表資料より pixel-to-ADC pipelined operetion説明図

私の興味ありリストに入れていませんが、本発表資料の格子の一つ

画素信号読み出し / AD変換&CDS / メモリからの信号読み出し の3つをパイプライン読み出し(=並列読み出し)している

という説明図。

まず、「今回の高速化の基本はこれですよ」という意図の説明だと思います。

ただ、予想で恐縮ですが、多かれ少なかれAptina以外の会社のセンサも同様のパイプライン処理は行っているのではと思います。

よって今回上図の詳細説明は割愛。

そしてここで③の”1行の読み出し時間が具体的に記されている”です。

上記パイプライン処理を考慮した、1行の読み出しに要する時間は、4.58uSecということです。

上図センサブロックダイヤグラム内で、有効画素数の行数が2712。

ざっくり1フレーム読み出すのに必要な時間は、4.58μSec×2712行≒0.0124Sec

1Sec/0.0124Sec≒80fps

ということで、当たり前ですがこのセンサのフレームレートと辻褄は合いそうです。

加えて本文中の文章でフォローすると

・このパイプライン処理によって、リセット及び信号レベルのサンプリングにそれぞれ1.6uSec(上図の”OS”及び”SIG”の期間にそれぞれ該当すると思われる)の時間を取ることが出来た

しかし、ここで”あれ?”となります。

上図では、1行目の信号を読み出したりしている最中に2行目のFDがリセットされている図になっています。

”これじゃ1行目の信号まともに読み出せないよ!(笑)”

何故なら1行目と2行目のFDは共通なのですから、どちらかの信号を読みたければ、FDはリセット出来ないからです。

と、内心小馬鹿にしていたら、間違いでは無く予想に反する回答(?)が載っていました。

↑発表資料より Nesting scanの読み出し方

※基本的に左の図をみるのがわかりやすいと思います。

その回答が④Nesting scan です。

画素のFDを縦方向の2画素で共有していることが前提です。←逆に言うと2画素で共有していなければこんな工夫は不要です。

3.4um□の微細な画素ピッチであるから必要な工夫と言い換えることも可能かもしれません。

つまり、上から順に行信号を読まずに、左上図の様に

#0(行目) ⇒ #2 ⇒ #1 ⇒ #3 ⇒ #4 ⇒ #6 ⇒ #5 ⇒ ・・・

という様に、FDを共有している画素行を続けて読むことが無いような走査順になっているのです!

(さきほどの水平方向でブロック毎に信号が読みだされてくることと合わせて)これまた何と後段でのデータ処理泣かせな(^^;)

ニコンという会社はどんな信号出力順でも、「後ろで並べ替えOKよ」という受けの広さを持っている様です。

これによるメリットは以下の様に具体的数字を持って示されています。

・従来のFDリセットの方法では、FDをリセットするのに(パルスのセトリングとそのばらつきも含めて)0.8~1uSecの時間を要した

⇒そんため、今回の(次に読む行は既にFDリセットされた状態からスタート出来る)Nesting scan方式では、リセット及び信号レベルのサンプリングにそれぞれ0.5uSecずつ時間を余計に割り振ることが可能になった

・同時に、もし仮に従来の方式のままであれば(0.5uSecずつ短い時間でリセットと信号レベルのサンプリングを行う必要があるため)約1.5倍の画素定電流と列アンプ定電流をそれぞれ流す必要があった。

⇒そのため、今回のNesting scan方式を取ることによって、同時に(同じ読み出しスピードを達成するのであれば)低消費電力化も図られている

今回、このNesting scanという(呼び方の名前の由来は不明ですが)読み出し順序の工夫に、私は一番衝撃を受けました。

その他、分光(量子効率)や、Dual Conversion Gain それぞれの際のノイズ及びその他の諸特性が報告されていますが、そちらは本論ではなさそうなので割愛。

最後に、低消費電力化を図られた後の各部の消費電力と、トータルの消費電力の他社比較が載せられています。

トータル1120mW。

今回、Nesting scan方式によって、読み出しスピードを高速化した割には消費電力の増大を抑えられたはずのAnalog(3.0V)ですが、それでもこの分類では最も電力食いな状態になっています。

まあデジタルと電源電圧が異なるので仕方が無いのでしょうか。

↑他社センサ比較

ちなみにこの[4]~[7]というのは引用文献の符番(?)となっており、調べるとそれぞれ以下の会社のセンサになっていました

[4]:Micron (マイクロン) 1085mW

※Aptinaはマイクロンのイメージセンサ部門が分社して出来た会社ですので、これが事実上の自社の以前のセンサ比

[5]ソニー 975mW ADCは分解能10bitのシングルスロープ方式

[6]ソニー 3000mW

[7]静岡大学×NHK×ブルックマンズテクノロジー 2670mW ADCはサイクリック方式

※どうも一番右端列の”FoM”という値は、画素数とフレームレートと出力bit数と消費電力とノイズを絡ませた指数の様です。

単純には上記値が”小さい方が良いセンサだ”と言いたい様です。

本発表資料の最後は(私の意訳では)ざっくり以下の様に締めくくっています。

「ハイエンドカメラとビデオに許容される(≒相応しい)特性の1インチセンサが出来た。

(上図を示して)他社と比較して、最も良いバランスのセンサだろう?」

比較対象の中で最も古いセンサが2010年に発表されたもの。今回のaptina報告のセンサと最大で3年の差があるのと、何となく上記”FoM”という指標が、”自社のセンサが最も有利になる指標にはどういうものがあるか?”という観点から逆に探し出したような胡散臭さを覚える指標であること

という二点の怪しさは感じなくもないですが、読み出しスピードに関して凄いセンサであることは間違い無い様に思います。

PR

コメント

シグナル処理速度

Nikon1の10.8Mと14Mセンサーは明らかにセンサー製造メーカーが異なっていますが、Chipworksは共にAptina製としています。AptinaがFabを変更したのかもしれません。

Nikon 1では高速読み出し後の画像生成だけでなく、撮像面位相差素子のシグナル処理も必要なので、画像処理チップは大変ですね。ニコンのExpeedは富士通Milbeautの専用カスタマイズ品だそうなので、富士通のエンジニアががんばったのでしょう。

Re:シグナル処理速度

>hi-lowさん

imagerマニアです。

・ニコン1の2種の画素数の異なるセンサの製造メーカーが異なる件

・ニコンの画像処理ICが富士通製な件

双方興味深い情報ありがとうございます。

前者の方の情報を素直に読むと、

「10.8Mの方は、マイクロンのFab製。しかし、14M品の方は画素ピッチが狭く、マイクロンFabでは(センサの微細プロセスにあまり投資していなくて最先端ではなく)十分な性能が出せないと判断し、どこか別のFabに製造委託した」

という様な感じでしょうか。

(※マイクロンがFabに投資していないというのは私の勝手な憶測です)

ブログ内検索

カウンター

最新コメント

[03/28 hoge]

[03/26 hi-low]

[03/22 山川]

[03/18 hoge]

[03/08 hi-low]

[03/04 hoge]

[02/26 山川]

[02/26 山川]

[02/19 hoge]

[02/18 山川]

[02/05 hoge]

[02/05 hi-low]

[01/29 通りすがりです]

[01/28 FT]

[01/23 hi-low]

カテゴリー

カレンダー

最新記事

(04/22)

(04/01)

(03/25)

(03/17)

(03/11)

最古記事

プロフィール

HN:

imagerマニア

性別:

非公開