Imager マニア

デジカメ / デジタルビデオカメラ / スマホ用の撮像素子(イメージセンサ/imager/CMOSセンサ)について、マニアな情報や私見を徒然なるままに述べるBlogです(^^;)

[PR]

×

[PR]上記の広告は3ヶ月以上新規記事投稿のないブログに表示されています。新しい記事を書く事で広告が消えます。

IISW 2017 プログラム発表 ~概観

また1週blog更新が空いてしましまいた。これももう一つ始めた老後の(?)趣味の悪影響か(^^;)

さて、この間、パナソニックに続き、日経新聞起因の今度はリコーの撤退騒動。

そしてパナソニック同様即座にリコーも火消し公式コメント発表。

しかし、カメラ事業に関してリコーが減損処理したことも事実の様子。

そして、発表資料のp.12には

”聖域を設けず、遠ざける事業の選別を徹底”

の項目の中に、

”トラディショナルカメラ”

が入っていますね。

”遠ざける事業”、”トラディショナルカメラ”・・・

どちらも個人的には初めて聞く用語です。相当言葉使いに気を遣ってる感じですね(^^;)

にしても、こういう発表内容で聞く”今年は構造改革を断行して、後に反転攻勢に出るための基礎体力を作る年”みたいな内容は、もう何年も前から日本の各電機系のメーカーで聞いた気がする内容ですね。相当既視感があります。場合によっては何年も言い続けてる会社もあるんじゃないかと思うくらい(^^;)

そして以前から思ってたのですが、日本って何で同業界の会社数が多いのでしょうか?

つまり、他国だと例えば電機メーカーで聞く名前といったら、その国で一つかせいぜい多くて二つ。

戦後の日本の復興過程とか国民性とかの影響なのでしょうか?

さて、この間、パナソニックに続き、日経新聞起因の今度はリコーの撤退騒動。

そしてパナソニック同様即座にリコーも火消し公式コメント発表。

しかし、カメラ事業に関してリコーが減損処理したことも事実の様子。

そして、発表資料のp.12には

”聖域を設けず、遠ざける事業の選別を徹底”

の項目の中に、

”トラディショナルカメラ”

が入っていますね。

”遠ざける事業”、”トラディショナルカメラ”・・・

どちらも個人的には初めて聞く用語です。相当言葉使いに気を遣ってる感じですね(^^;)

にしても、こういう発表内容で聞く”今年は構造改革を断行して、後に反転攻勢に出るための基礎体力を作る年”みたいな内容は、もう何年も前から日本の各電機系のメーカーで聞いた気がする内容ですね。相当既視感があります。場合によっては何年も言い続けてる会社もあるんじゃないかと思うくらい(^^;)

そして以前から思ってたのですが、日本って何で同業界の会社数が多いのでしょうか?

つまり、他国だと例えば電機メーカーで聞く名前といったら、その国で一つかせいぜい多くて二つ。

戦後の日本の復興過程とか国民性とかの影響なのでしょうか?

PR

Nikon D500 搭載 APS-C 2000万画素CMOSイメージセンサはソニー製【確定】 ~それと1億画素及び1.5億画素中判センサと

現役”名人”が、最強コンピューターには負ける昨今、

それと比較すれば驚くには値しない(?)のだと思いますが、

ソニー

1億画素 3.6インチ 裏面照射型センサ

及び

1.5億画素 4.2インチ 裏面照射型センサ

を、2018年リリース予定

sourceは例によってimageSensorsWorldさんですが、

一次ソースは、何かの展示会の様なイベントのソニーブースのソニー社員と思われる方が、

パネルを元に返答されていますので、

噂とかでなく信用できる情報の様子ですね。

↑左は(恐らく)3.6インチ 1億画素、右は(恐らく)4.2インチ 1.5億画素 表面照射型センサ

上の写真のセンサは、まだBSIでは無い現行生産モデルの様子

しかし、持っている方の指の大きさと比較すると、やはりこのサイズになると本当に大きいですね(^^;)

それと比較すれば驚くには値しない(?)のだと思いますが、

ソニー

1億画素 3.6インチ 裏面照射型センサ

及び

1.5億画素 4.2インチ 裏面照射型センサ

を、2018年リリース予定

sourceは例によってimageSensorsWorldさんですが、

一次ソースは、何かの展示会の様なイベントのソニーブースのソニー社員と思われる方が、

パネルを元に返答されていますので、

噂とかでなく信用できる情報の様子ですね。

↑左は(恐らく)3.6インチ 1億画素、右は(恐らく)4.2インチ 1.5億画素 表面照射型センサ

上の写真のセンサは、まだBSIでは無い現行生産モデルの様子

しかし、持っている方の指の大きさと比較すると、やはりこのサイズになると本当に大きいですね(^^;)

Lumix GH5について ~パナソニック デジカメ事業など再リストラの報道に絡んで徒然と

"パナソニック、再リストラ デジカメなど6事業"

ここを見に来られる様な皆さんなら既にご存知のことと思いますが、

冒頭の見出しは昨日の日経の一面記事タイトルです。

パナソニックの公式発表では無いと思いますが、

だいたいこういうのは「弊社では何も決まった事実はありません」と一旦否定しておいて、数日後に公式発表という流れなのだと思います。

(まあ今回の内容は、対外的に発表する必要が必ずある内容でも無いので、何の発表も無いということはあり得ますが・・・)

で、”じゃあ一体どこまでリストラ?”

というのがエンドユーザーとしては気になるところなのですが、

この記事から断定的なことが言える情報は無いと思いますので、もちろん以下私個人の予想ですが、

・GHシリーズ以上、及び業務用のカムコーダーは(組織形態が変わってたとしても)今まで通り継続

・イメージセンサ事業も同様に継続

上記は、パナソニックがB to B事業は強化する方針だと読み聞きしていて、

そして上記分野はB to B事業に該当するだろうと思うからです。

イメージセンサに関しては、そもそも記事に触れられている6事業に入ってないんじゃないかと思いますし、

近年、特に有機撮像素子に関しては熱心で、開発もリードしている様に見受けられますし、

そもそも用途がデジカメ用だけでなく(←というか、近年はデジカメ用にパナソニックの素子はほとんど出回ってないのでは?)、車載や産業用などは正にB to B事業そのものだからです。

キヤノン 外販用グローバルシャッタCMOSイメージセンサ(と思われる) ~ISSCC2017より

また一週blog更新が空いてしまいました(^^;)

今年も早いもので、もう卒業・入学式シーズン。日本ではカメラが最も売れる時(?)でしょうか?

という訳でも無いでしょうが、ワールドワイドでは今年の1月は近年稀に見る絶好調なカメラの販売状況(正確には出荷状況ですが)の様子です。

レンズ交換式カメラに至っては、前年同月比プラスに加えて、2年前の'15年1月をも上回った様です。

コンパクトデジカメの減少幅も約7%と、こちらも各社年間通した想定減少幅と比べれば、恐らく小さな値で収まっていそう。

恐らくデジカメ分野は、民生用途のイメージセンサ市場としては、スマホ、タブレット&pcに次ぐ3番目に大きな市場だと思いますので(←違いますかね?)結構なことだと思います(^^)

今回は、まず2回前の弊blogのソニーの3層積層型イメージセンサに関する記載の訂正から(^^;)

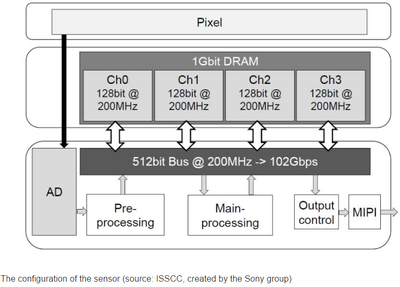

↑日経のサイトから。図の下の記載から、大元の出典はソニーの今年のISSCCの恐らくプレゼン資料から

3層積層センサのデータフロー図

既にコメント欄で情報及びご指摘頂いていますが、私は2回前のエントリで、

「DRAMへのアクセスはセンサ基板とロジック基板双方から行っているのだからDRAMを真ん中の層へ配置するのは何が疑問なんだろう?」

という様なニュアンスのコメントを書きました。

しかし、上図を見ると、(というか、上図を見ずとも過去のソニーの積層センサの多くは、)列ADC回路をbottomのロジック基板に配置してあるため、

データフローとしては、イメージセンサからのアナログ信号をロジック基板にまず通してしまうので、

その後、センサ基板(フォトダイオード配置基板)からDRAMに何かアクセスする必要性が発生しません。

故に、私の上記記載は、DRAM基板が真ん中に配置される理由には全くなり得ないことがわかります。

であるならば、後は私が思いつくDRAMが真ん中に配置される必然性と言えば、

今年も早いもので、もう卒業・入学式シーズン。日本ではカメラが最も売れる時(?)でしょうか?

という訳でも無いでしょうが、ワールドワイドでは今年の1月は近年稀に見る絶好調なカメラの販売状況(正確には出荷状況ですが)の様子です。

レンズ交換式カメラに至っては、前年同月比プラスに加えて、2年前の'15年1月をも上回った様です。

コンパクトデジカメの減少幅も約7%と、こちらも各社年間通した想定減少幅と比べれば、恐らく小さな値で収まっていそう。

恐らくデジカメ分野は、民生用途のイメージセンサ市場としては、スマホ、タブレット&pcに次ぐ3番目に大きな市場だと思いますので(←違いますかね?)結構なことだと思います(^^)

今回は、まず2回前の弊blogのソニーの3層積層型イメージセンサに関する記載の訂正から(^^;)

↑日経のサイトから。図の下の記載から、大元の出典はソニーの今年のISSCCの恐らくプレゼン資料から

3層積層センサのデータフロー図

既にコメント欄で情報及びご指摘頂いていますが、私は2回前のエントリで、

「DRAMへのアクセスはセンサ基板とロジック基板双方から行っているのだからDRAMを真ん中の層へ配置するのは何が疑問なんだろう?」

という様なニュアンスのコメントを書きました。

しかし、上図を見ると、(というか、上図を見ずとも過去のソニーの積層センサの多くは、)列ADC回路をbottomのロジック基板に配置してあるため、

データフローとしては、イメージセンサからのアナログ信号をロジック基板にまず通してしまうので、

その後、センサ基板(フォトダイオード配置基板)からDRAMに何かアクセスする必要性が発生しません。

故に、私の上記記載は、DRAM基板が真ん中に配置される理由には全くなり得ないことがわかります。

であるならば、後は私が思いつくDRAMが真ん中に配置される必然性と言えば、

CP+2017 ~今年のテーマは何だろう?(^^;)

ブログ内検索

カウンター

最新コメント

[03/28 hoge]

[03/26 hi-low]

[03/22 山川]

[03/18 hoge]

[03/08 hi-low]

[03/04 hoge]

[02/26 山川]

[02/26 山川]

[02/19 hoge]

[02/18 山川]

[02/05 hoge]

[02/05 hi-low]

[01/29 通りすがりです]

[01/28 FT]

[01/23 hi-low]

カテゴリー

カレンダー

最新記事

(04/22)

(04/01)

(03/25)

(03/17)

(03/11)

最古記事

プロフィール

HN:

imagerマニア

性別:

非公開