Imager マニア

デジカメ / デジタルビデオカメラ / スマホ用の撮像素子(イメージセンサ/imager/CMOSセンサ)について、マニアな情報や私見を徒然なるままに述べるBlogです(^^;)

[PR]

×

[PR]上記の広告は3ヶ月以上新規記事投稿のないブログに表示されています。新しい記事を書く事で広告が消えます。

ISSCC 2018 SONY 14bit画素AD搭載 146万画素裏面積層型グローバルシャッタセンサ

CP+が今年も終了・・・

ですが、遂に今年は行けませんでした(--;)

振り返ってみると、恐らく前回行かなかったのは2011年。

7年連続とはなりませんでした。

ただ、7年前と異なるのはyoutube全盛のご時世。確か7年前はyoutubeはまださほど広まっていなかったような・・・

という訳で、今年のCP+はyoutube見て我慢することにします。

さて、今年2月サンフランシスコでのISSCC

ネットで無料記事がいくつか出回っていますね。

その中で、イメージセンサー案件でトップバッターでの発表であり、また最注目案件であったと思われるソニーの146万画素 画素AD搭載センサについて、サラッと残しておきたいと思います。

↑EETimesより

ですが、遂に今年は行けませんでした(--;)

振り返ってみると、恐らく前回行かなかったのは2011年。

7年連続とはなりませんでした。

ただ、7年前と異なるのはyoutube全盛のご時世。確か7年前はyoutubeはまださほど広まっていなかったような・・・

という訳で、今年のCP+はyoutube見て我慢することにします。

さて、今年2月サンフランシスコでのISSCC

ネットで無料記事がいくつか出回っていますね。

その中で、イメージセンサー案件でトップバッターでの発表であり、また最注目案件であったと思われるソニーの146万画素 画素AD搭載センサについて、サラッと残しておきたいと思います。

↑EETimesより

恐らく、上記リンク先が見つけた中では一番詳しい情報が載っていそうでしょうか。

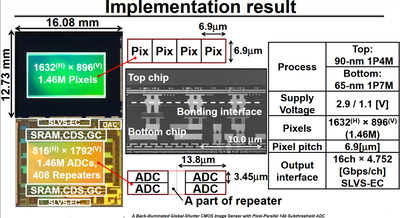

そして、上記写真は、恐らく体裁からすると、実際の発表スライド写真の様な気がします。

プロセス:top基板 90nm 1P4M (←1層polySi / 4層メタル)

bottom基板 65nm 1P7M (同上)

供給電圧:2.9V / 1.1V

画素数 :1632 × 896 ≒ 146万画素

画素ピッチ:6.9um

出力インターフェース:SLVS-EC 16ch × 4.753 Gbps/ch

チップサイズ:16.08 × 12.73mm

bottom基板にはSRAMも搭載されていること

また、top基板で横1x4画素分が、

bottom基板では1画素分が13.8um×3.45umという長方形区画に1画素分のADCが配置されて、

それが2x2で並んでtop基板の画素と対応取っているみたいですね。

恐らく画素ADのレイアウトの都合上、正方形区画よりも上記の様な長方形区画の方が配置し易かったということでしょうか。

使用プロセスは、以前からソニーが学会発表されている様なセンサーで使っている世代のものから微細度合いは変わらない様に見えます。

後でリンクを貼るページの記述と、上図発表資料を併せて見ると、

今回本当に1画素に1ADCを割り当てている本物の?画素AD搭載で、かつそのADの分解能が14bitとかなりな高分解能なものであるため、

ADが配置されているbottom基板はプロセスの世代が一つ進むかなという気もしていましたが、それはどうもそうでは無かった様です。

しかし本当に6.9um□の面積に14bitAD入るんですね~

あとは出力インターフェースの1chあたり4.753Gbpsは無茶苦茶速いですね。

ここだけ見たらもうCPUかっていうくらい(^^;)

あとは、供給電圧の2.9Vと1.1Vですが、

普通に考えると、前者がアナログ回路用で後者がデジタル回路用だと思いますが、

特に後者のデジタル回路用と思われる電源の1.1Vというのはあまり耳慣れない数字・・・

多くの場合1.2Vということが多いのではと思うのですが、

これは画素AD搭載でどうしても消費電力が大きくなるのを、トータルで少しでも電力消費を抑えるために電源電圧を0.1V削ったという様な雰囲気でしょうか。

上記スライド?から読み取れるのは、こんなところでしょうか?

↑同じくEETimesより

フレームレート660fpsは、画素数146万画素であれば、例え14bit分解能であったとしても、ソニーさんとしては特に驚く様なスペックでは無い感じでしょうか。

以前既に4Kで480fpsという様なセンサも発表していますしね。

まあ画素ADと列ADでは勝手が違うかもしれないので単純比較して良いのかわかりませんが・・・

飽和電子数の16600電子というのは・・・

6.9umという画素ピッチを考慮すると、むしろかなり小さい感じですね(^^;)

続けてしまうと、

感度 :61500e-/lx・s

PLS :-75dB

コンバージョンゲイン:60uV/e-

ダイナミックレンジ :70.2dB

ランダムノイズ :5.15e-rms

というのも、いずれもISSCCの学会発表センサという目で見ると・・・

少なくともこのスペックが元になってISSCC採用が決まったという様な数字では無さそうです(^^;)

まあPLSは、今回は”裏面照射型の”グローバルシャッタセンサということで、

今までの多くの表面照射型グローバルシャッタセンサと同じ土俵で比べるのは酷だとは思いますが・・・

そしてランダムノイズもアナログゲイン0dBという条件下で比較すれば良い値なのかもしれませんが・・・

で、”じゃあ何がスゴいのさ?”というところで、

それはやっぱり上図赤枠内の、

コンパレータの駆動時消費電流:111nA

消費電力:746mW

の二つですよね。

111nA・・・つまり0.111uAということですが、コンパレータってこんな小さな電流でまともに動くものなんでしょうか?(^^;)

これが今回タイトルにも入っている”サブスレッショルドADC”なるものの効果であろうとは予測できるのですが、残念ながら見つけた記事の中でこのサブスレッショルドADCの部分に触れたものはありませんでした。

まあ記者の方も決められた文字数の中でこのADCの部分の説明を断念したか、読者の興味の範囲を外れると判断したか、はたまた記者が理解できなかったか(^^;)

とにかく諸般の事情でなかなか記事には出来ないのでしょうね。

で、結果としての消費電力746mW。

これも単純に”146万画素のセンサ”という目で見たら、小さな値では無いと思うのですが、

146万もの14bit分解能のADCが動いていると考えるとかなり小さな値に感じます。

来週もう少しだけ本件エントリ続けるかもしれませんが、

本日はこの辺でおしまいにします。

そして、上記写真は、恐らく体裁からすると、実際の発表スライド写真の様な気がします。

プロセス:top基板 90nm 1P4M (←1層polySi / 4層メタル)

bottom基板 65nm 1P7M (同上)

供給電圧:2.9V / 1.1V

画素数 :1632 × 896 ≒ 146万画素

画素ピッチ:6.9um

出力インターフェース:SLVS-EC 16ch × 4.753 Gbps/ch

チップサイズ:16.08 × 12.73mm

bottom基板にはSRAMも搭載されていること

また、top基板で横1x4画素分が、

bottom基板では1画素分が13.8um×3.45umという長方形区画に1画素分のADCが配置されて、

それが2x2で並んでtop基板の画素と対応取っているみたいですね。

恐らく画素ADのレイアウトの都合上、正方形区画よりも上記の様な長方形区画の方が配置し易かったということでしょうか。

使用プロセスは、以前からソニーが学会発表されている様なセンサーで使っている世代のものから微細度合いは変わらない様に見えます。

後でリンクを貼るページの記述と、上図発表資料を併せて見ると、

今回本当に1画素に1ADCを割り当てている本物の?画素AD搭載で、かつそのADの分解能が14bitとかなりな高分解能なものであるため、

ADが配置されているbottom基板はプロセスの世代が一つ進むかなという気もしていましたが、それはどうもそうでは無かった様です。

しかし本当に6.9um□の面積に14bitAD入るんですね~

あとは出力インターフェースの1chあたり4.753Gbpsは無茶苦茶速いですね。

ここだけ見たらもうCPUかっていうくらい(^^;)

あとは、供給電圧の2.9Vと1.1Vですが、

普通に考えると、前者がアナログ回路用で後者がデジタル回路用だと思いますが、

特に後者のデジタル回路用と思われる電源の1.1Vというのはあまり耳慣れない数字・・・

多くの場合1.2Vということが多いのではと思うのですが、

これは画素AD搭載でどうしても消費電力が大きくなるのを、トータルで少しでも電力消費を抑えるために電源電圧を0.1V削ったという様な雰囲気でしょうか。

上記スライド?から読み取れるのは、こんなところでしょうか?

↑同じくEETimesより

フレームレート660fpsは、画素数146万画素であれば、例え14bit分解能であったとしても、ソニーさんとしては特に驚く様なスペックでは無い感じでしょうか。

以前既に4Kで480fpsという様なセンサも発表していますしね。

まあ画素ADと列ADでは勝手が違うかもしれないので単純比較して良いのかわかりませんが・・・

飽和電子数の16600電子というのは・・・

6.9umという画素ピッチを考慮すると、むしろかなり小さい感じですね(^^;)

続けてしまうと、

感度 :61500e-/lx・s

PLS :-75dB

コンバージョンゲイン:60uV/e-

ダイナミックレンジ :70.2dB

ランダムノイズ :5.15e-rms

というのも、いずれもISSCCの学会発表センサという目で見ると・・・

少なくともこのスペックが元になってISSCC採用が決まったという様な数字では無さそうです(^^;)

まあPLSは、今回は”裏面照射型の”グローバルシャッタセンサということで、

今までの多くの表面照射型グローバルシャッタセンサと同じ土俵で比べるのは酷だとは思いますが・・・

そしてランダムノイズもアナログゲイン0dBという条件下で比較すれば良い値なのかもしれませんが・・・

で、”じゃあ何がスゴいのさ?”というところで、

それはやっぱり上図赤枠内の、

コンパレータの駆動時消費電流:111nA

消費電力:746mW

の二つですよね。

111nA・・・つまり0.111uAということですが、コンパレータってこんな小さな電流でまともに動くものなんでしょうか?(^^;)

これが今回タイトルにも入っている”サブスレッショルドADC”なるものの効果であろうとは予測できるのですが、残念ながら見つけた記事の中でこのサブスレッショルドADCの部分に触れたものはありませんでした。

まあ記者の方も決められた文字数の中でこのADCの部分の説明を断念したか、読者の興味の範囲を外れると判断したか、はたまた記者が理解できなかったか(^^;)

とにかく諸般の事情でなかなか記事には出来ないのでしょうね。

で、結果としての消費電力746mW。

これも単純に”146万画素のセンサ”という目で見たら、小さな値では無いと思うのですが、

146万もの14bit分解能のADCが動いていると考えるとかなり小さな値に感じます。

来週もう少しだけ本件エントリ続けるかもしれませんが、

本日はこの辺でおしまいにします。

PR

ブログ内検索

カウンター

最新コメント

[03/28 hoge]

[03/26 hi-low]

[03/22 山川]

[03/18 hoge]

[03/08 hi-low]

[03/04 hoge]

[02/26 山川]

[02/26 山川]

[02/19 hoge]

[02/18 山川]

[02/05 hoge]

[02/05 hi-low]

[01/29 通りすがりです]

[01/28 FT]

[01/23 hi-low]

カテゴリー

カレンダー

最新記事

(04/22)

(04/01)

(03/25)

(03/17)

(03/11)

最古記事

プロフィール

HN:

imagerマニア

性別:

非公開