Imager マニア

デジカメ / デジタルビデオカメラ / スマホ用の撮像素子(イメージセンサ/imager/CMOSセンサ)について、マニアな情報や私見を徒然なるままに述べるBlogです(^^;)

[PR]

×

[PR]上記の広告は3ヶ月以上新規記事投稿のないブログに表示されています。新しい記事を書く事で広告が消えます。

IISW2017 TechInsights ~その2:ウェハ to ウェハの相互接続とその他の積層チップの特徴について またα9搭載撮像素子は12行ごと読み出し

5月のCIPA発表のデジカメ出荷台数発表

日本は微妙みたいですが、ワールドワイドで見れば、かつ対前年度比で言えば、

絶好調の結果だったみたいですね・・・まあ昨年5月と言えば、微妙に熊本の震災の影響(主にソニー撮像素子工場被災によるイメージセンサ出荷停止)を受け始めた月ではありますが(^^;)

この後夏場はしばらくは対前年度比増の結果が出て、最後冬場に昨年並みの出荷台数をキープできるかどうかによって、年間ベースで昨年台数実績を上回れるか否かが決まるという感じではないでしょうか。

今年は昨年に比べて、レンズ交換式カメラに関してはエントリー機の発売が多い感じですので、台数ベースで言えばレンズ交換式に関しては昨年実績を達成できそうな気が個人的にはします。

あとはコンパクトデジカメ次第といった感じでしょうか。

別件ですが、dpreviewがソニーα9の電子シャッターモードにおいて、

LEDフリッカー起因の12行ごとの周期的な縞が出る報告をしている様ですね。

これがどの程度の頻度で出るものなのか?

これがプロスポーツカメラマンにとってどの程度致命的なものなのか?

個人的には興味のあるところですが、imagerマニアとして興味のあるdpreview分析(?)コメントが以下。

α9(の電子シャッター駆動時は)

◆12行ごと(≒同時)読み出し

◆1フレームを6.25m秒で読みだしている

日本は微妙みたいですが、ワールドワイドで見れば、かつ対前年度比で言えば、

絶好調の結果だったみたいですね・・・まあ昨年5月と言えば、微妙に熊本の震災の影響(主にソニー撮像素子工場被災によるイメージセンサ出荷停止)を受け始めた月ではありますが(^^;)

この後夏場はしばらくは対前年度比増の結果が出て、最後冬場に昨年並みの出荷台数をキープできるかどうかによって、年間ベースで昨年台数実績を上回れるか否かが決まるという感じではないでしょうか。

今年は昨年に比べて、レンズ交換式カメラに関してはエントリー機の発売が多い感じですので、台数ベースで言えばレンズ交換式に関しては昨年実績を達成できそうな気が個人的にはします。

あとはコンパクトデジカメ次第といった感じでしょうか。

別件ですが、dpreviewがソニーα9の電子シャッターモードにおいて、

LEDフリッカー起因の12行ごとの周期的な縞が出る報告をしている様ですね。

これがどの程度の頻度で出るものなのか?

これがプロスポーツカメラマンにとってどの程度致命的なものなのか?

個人的には興味のあるところですが、imagerマニアとして興味のあるdpreview分析(?)コメントが以下。

α9(の電子シャッター駆動時は)

◆12行ごと(≒同時)読み出し

◆1フレームを6.25m秒で読みだしている

リンク先に掲載されている写真では12行ごとの縞なのか確認できませんが(dpreviewにはオリジナル写真あるのかもしれません)、それが12行ごとに出ているとするならば、

12行同時読み出しという分析は正しい可能性がかなり高そうですね。

後者の6.25mSecの算出の仕方はリンク先には記載されていませんが、

明滅周期のわかっている光源を連写するとか、本格的にやりたければ例えばこの写真の右下の様な装置を持っていればある程度正確に測定可能で、

そしてdpreviewであればそんな装置でも持っているでしょうから、この分析数字も信じて良さそうでしょうかね。

とすると、(実際のカメラとしてはそのスピードで連写記録は出来ないものの、イメージセンサ単体の画素信号読み出しフレーム数の実力としては)α9搭載撮像素子は、

◆1Sec ÷ 6.25mSec = 160fps

ソニー公称のα9の読み出し速度は、”従来比20倍以上”ということで、

仮に同じフルサイズミラーレスのα7系が概ね5fpsで、それの20倍だと100fps。

上記前提条件だと公称値との乖離が大きい様にも思いますが、元々”以上”という表現であったというのと、

そもそももしかしたらα7系カメラの連写速度がメカシャッター律速で決まっていた可能性も否定出来ない気もしますので、

dpreview記載の6.25mSec/1フレームの数字もあり得る範囲な気がしますね。

逆に言うと、もしかしたらα7系搭載センサ単体の読み出し速度の実力は

160÷20=8fps

程度あったという可能性も!?

いずれにしても、α9搭載ソニー製撮像素子単体の実力は100fps以上あろうことは、(ソニーのローリングシャッター歪の小ささへの自信を考慮しても)もうほぼ間違い無いと思います。

2400万画素のフルサイズセンサを・・・

いやはや凄い技術の進歩と時代になったものです(^^;)

後者の12行同時読み出しというのは、過去に既にソニーのDRAM積層撮像素子で”8行同時読み相当(≒恐らく4列に8本の垂直信号線が存在)”というセンサはありましたし、

過去に純粋に1列に2本の垂直信号線が存在したというセンサもありましたが、

12本の垂直信号線というのは・・・

その数字の半端さも手伝って異様です(^^;)

しかし、DRAM積層センサが1.22um×4=4.88um□に8本読み出し線をレイアウト可能なら、

フルサイズ2400万画素(≒横36mmで6000列)≒約6umの画素ピッチに12本の縦配線を配置することは、

(元来垂直信号線以外にも配置しなければならない配線があるだろうことを考慮すれば、)同じレベルの微細プロセス使用のままでもなんとか可能な範囲でしょうか。

もしくは単純にセンサ基板の配線総数が、DRAM積層センサよりもα9搭載撮像素子の方が多いという可能性もありますか。

いずれにしても、配線による光線蹴られを気にしなくても良い裏面照射型センサの恩恵の内の一つであることは間違い無さそうです。

さて、以下からは今週の本題。

IISW2017におけるTechInsightsのレポートblogのPart.2です

Part2は、主に積層センサとその積層の接続方法に関するものの様です。

12行同時読み出しという分析は正しい可能性がかなり高そうですね。

後者の6.25mSecの算出の仕方はリンク先には記載されていませんが、

明滅周期のわかっている光源を連写するとか、本格的にやりたければ例えばこの写真の右下の様な装置を持っていればある程度正確に測定可能で、

そしてdpreviewであればそんな装置でも持っているでしょうから、この分析数字も信じて良さそうでしょうかね。

とすると、(実際のカメラとしてはそのスピードで連写記録は出来ないものの、イメージセンサ単体の画素信号読み出しフレーム数の実力としては)α9搭載撮像素子は、

◆1Sec ÷ 6.25mSec = 160fps

ソニー公称のα9の読み出し速度は、”従来比20倍以上”ということで、

仮に同じフルサイズミラーレスのα7系が概ね5fpsで、それの20倍だと100fps。

上記前提条件だと公称値との乖離が大きい様にも思いますが、元々”以上”という表現であったというのと、

そもそももしかしたらα7系カメラの連写速度がメカシャッター律速で決まっていた可能性も否定出来ない気もしますので、

dpreview記載の6.25mSec/1フレームの数字もあり得る範囲な気がしますね。

逆に言うと、もしかしたらα7系搭載センサ単体の読み出し速度の実力は

160÷20=8fps

程度あったという可能性も!?

いずれにしても、α9搭載ソニー製撮像素子単体の実力は100fps以上あろうことは、(ソニーのローリングシャッター歪の小ささへの自信を考慮しても)もうほぼ間違い無いと思います。

2400万画素のフルサイズセンサを・・・

いやはや凄い技術の進歩と時代になったものです(^^;)

後者の12行同時読み出しというのは、過去に既にソニーのDRAM積層撮像素子で”8行同時読み相当(≒恐らく4列に8本の垂直信号線が存在)”というセンサはありましたし、

過去に純粋に1列に2本の垂直信号線が存在したというセンサもありましたが、

12本の垂直信号線というのは・・・

その数字の半端さも手伝って異様です(^^;)

しかし、DRAM積層センサが1.22um×4=4.88um□に8本読み出し線をレイアウト可能なら、

フルサイズ2400万画素(≒横36mmで6000列)≒約6umの画素ピッチに12本の縦配線を配置することは、

(元来垂直信号線以外にも配置しなければならない配線があるだろうことを考慮すれば、)同じレベルの微細プロセス使用のままでもなんとか可能な範囲でしょうか。

もしくは単純にセンサ基板の配線総数が、DRAM積層センサよりもα9搭載撮像素子の方が多いという可能性もありますか。

いずれにしても、配線による光線蹴られを気にしなくても良い裏面照射型センサの恩恵の内の一つであることは間違い無さそうです。

さて、以下からは今週の本題。

IISW2017におけるTechInsightsのレポートblogのPart.2です

Part2は、主に積層センサとその積層の接続方法に関するものの様です。

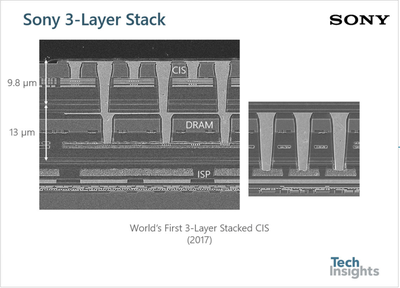

Stacked Chip Image Sensors

積層センサにおいては、

・低温でのウェハ接続方法

・ウェハ to ウェハの相互接続技術

の2つの開発が鍵

スマホカメラチップにおいては、

”裏面照射型センサ と ISP(mixed-signal image processor)の2つのチップ積層”

が最も一般的な積層形態

CIS部には有効画素アレイのみ

他方、大半の信号処理・デジタル演算処理系はISPチップに載せられることが多い

A. STACKED CHIP FABRICATION TECHNOLOGY TREND

・最近の積層センサの裏面照射型センサチップの製造トレンドは、安定的に90nmないしは65nmプロセス世代

・これは、CISチップにおいては、スケーリングする必要性があまり無いためだが、

最近は、1.0um世代の画素構造において、狭いW(タングステン)開口grid製造のために、65nm未満のプロセスが用いられていることが確認されている

・サムスンの28nmのhigh-K(高誘電率ゲート絶縁膜)メタルゲートプロセスが、最近積層のISPチップにて用いられた

・今後もISPチップ使用プロセスについては、先端CMOSプロセスが採用され続けることが予想される

最近は、センサ画素部にも65nm未満のプロセスが用いられることがあるのですか。

そう言えば過去唯一記憶のある限りでは、NHKとTSMC製造の8K240fps2/3インチイメージセンサのセンサ部が45nmプロセス使用でした。

ただ、iPhoneやGalaxyカメラ搭載のソニー製/Sumsung製撮像素子の積層のセンサチップについては、記載が無いだけで、65nm未満の製造プロセスが用いられている可能性もあるかもしれませんね。

そしてISPチップの方の28nmプロセス使用の実績があるのは恐らく私は初耳です。

世の中の最先端CMOSプロセスでは、現在16nm/14nm世代で量産実績があり、今年後半に順調にいけば10nmプロセスが立ち上がる状況なので、28nm世代は数世代古いプロセス世代とは言え、それでもイメージャーで既に28nmプロセス使用実績があろうとは・・・

しかし、TechInsightsの予想では、今後は28nmプロセスより更に先端プロセス使用の方向へ向かうというニュアンスの記載がありますが、

個人的にはこれには少し懐疑的です。

受け売りで詳しい訳では無いですが、20nm世代以降のプロセスはコストアップが急激に進み、かなりの量産規模を誇るチップしかそのスケーリングメリットを享受出来なくなると様々なところで書かれています。

もちろん半導体業界なので5年先とかにはそれでも移行しているとは思いますが、ここ1~2年の間はどうなのでしょうか?

出来てもiPhoneとGalaxyに採用が決まっている撮像素子しか使えないとかそういうことになっているのではないでしょうか?

また、上の表の2015年のOmnivisionの製造Fabの”XMC”というのに注目です。

私は例によってImageSensorsWorldsさんの記事で知ったのですが、

恐らくOmnivisionが中国系のHua Capitalに買われた頃がキッカケになって、TSMCからイメージセンサの製造Fabを乗り換えたりし始めている、大陸のFabです。

上表では2016年には再びTSMCの同世代プロセス製にOmnivisionのセンサが戻っているので、まだTSMCに対して技術レベルに差があるのかもしれませんが、

恐らくのところ、TSMCよりもXMCなるところの方がモノ自体は安く作れるのじゃないのかなと(私が勝手に)予想しています。

という訳で、Omnivisionの製造Fabがどうなっていくのか、個人的には注目しています。

B. WAFER-TO-WAFER INTERCONNECT

市場に最も早く積層CMOSイメージセンサを投入したのはソニーだった

2013年に、oxide(酸化膜) bonding とTSVを用いたwafer to wafer の貼り合わせを行い、

その後2016年に、”Cu2Cuボンディング” もしくは”DBI”として知られる、Cu-to-Cuハイブリッドボンディングを実用化した

第一世代のTSV(上写真a)は、

・1.12um画素アレイの両側と上側に沿って、主に3つのアレイが

・dual TSV構造を特徴とした (aの写真の様に、上下のそれぞれのノードをつなぐために、それぞれに一つずつの穴を開けて、上側で最終的に導通させる構造を指すと思われる)

・一つは浅く、Cu(銅)で埋められたTSVが、CISのメタル1層パッドの裏側と接続され

一つは深く、やはりCuで埋められたTSVが、ISPチップのAL(アルミ)パッドと接続され

最終的にはそれらが平面のCuメタルによって接続されている

・Dual TSVのフットプリント(=上面から見た形状)は長方形で、

6.0um × 9.0um のピッチで配置されていた

ソニーはその後、2015年にTSVプロセスフローを簡略化した(上写真b)

CISとISPのパッドを、一つの円筒形のTSVで垂直に相互接続させた

このTSVはハーフピッチで千鳥にずらして配置されていたけれども、ミニマムピッチは9.1umだった

Omnivision初の積層チップ(上図a)は、

・pureCel-Cプラットフォームで、XMCによって製造されたもの

・幅広の一つの穴で、CISとISPのパッドを接続する構造を特徴とする

・1.12um画素世代チップで使われ

・フットプリントは長方形で

・5.2um × 9.9umのピッチで配置されていた

その後、Omnivisionは、以下の様なTSVを採用した(上図b)

・TSMC製で

・ソニー同様一つのまっすぐな穴のTSV構造

・1.0um画素ピッチ世代のセンサにおいて

・配置ピッチは4.0 x 4.0um

Samsungの積層チップでは、やはりOmni同様のTSVが見れらた(上図c)

しかし、決定的に異なるのは、W(タングステン)ベースの空洞TSV

(つまり写真の様に穴の内側表面だけWで覆われていて、中身は空洞という・・・)

第一世代のSamsung TSVは

・1.12um画素ピッチ世代のチップに採用され

・TSVの配置ピッチは8.8um × 9.6um

ソニーは最近ウェハの相互接続戦略(?)を

TSVアレイから、DBI接続に置き換えるように

シフトしてきた (2つ上の写真のc)

実際に電気的に相互接続に用いられるDBIパッドは、TSVが配置されていたのと同じ領域に配置され、

ダミーのDBIパッドは、有効画素領域と周辺領域のほぼすべての領域に配置されている

(↑ダミーのDBIパッドがかなりの領域に配置されているのは、個人的にはウェハ貼り合わせ前のCMP研磨による平坦性確保の観点からではないかと予想しています)

現在のDBIパッドは、

・幅3umの正方形

・配置ピッチは6um

現在、(少なくともイメージセンサで製品化はされていないが、最小で)1.6umピッチのDBIが報告されている。

将来、画素単位で相互接続可能になることが期待されている

以上でテックインサイトのPart2ブログは終了です。

後半のTSVなどの具体的な接続方法に関してのくだりは、すべて過去同じくチップワークスblog等で公表済みのものだったのかなと思います。

個人的には以前も弊blogで書きましたが、

Samsungの空洞のTSVに関しては、機械的な強度?がどうなのか気になります(^^;)

PR

コメント

ブログ内検索

カウンター

最新コメント

[03/28 hoge]

[03/26 hi-low]

[03/22 山川]

[03/18 hoge]

[03/08 hi-low]

[03/04 hoge]

[02/26 山川]

[02/26 山川]

[02/19 hoge]

[02/18 山川]

[02/05 hoge]

[02/05 hi-low]

[01/29 通りすがりです]

[01/28 FT]

[01/23 hi-low]

カテゴリー

カレンダー

最新記事

(04/22)

(04/01)

(03/25)

(03/17)

(03/11)

最古記事

プロフィール

HN:

imagerマニア

性別:

非公開